2 block diagram of 8-/16-bit ppg timer d, Block diagram of 8-/16-bit ppg timer d – FUJITSU F2MCTM-16LX User Manual

Page 304

288

CHAPTER 16 8-/16-BIT PPG TIMER

16.2.2

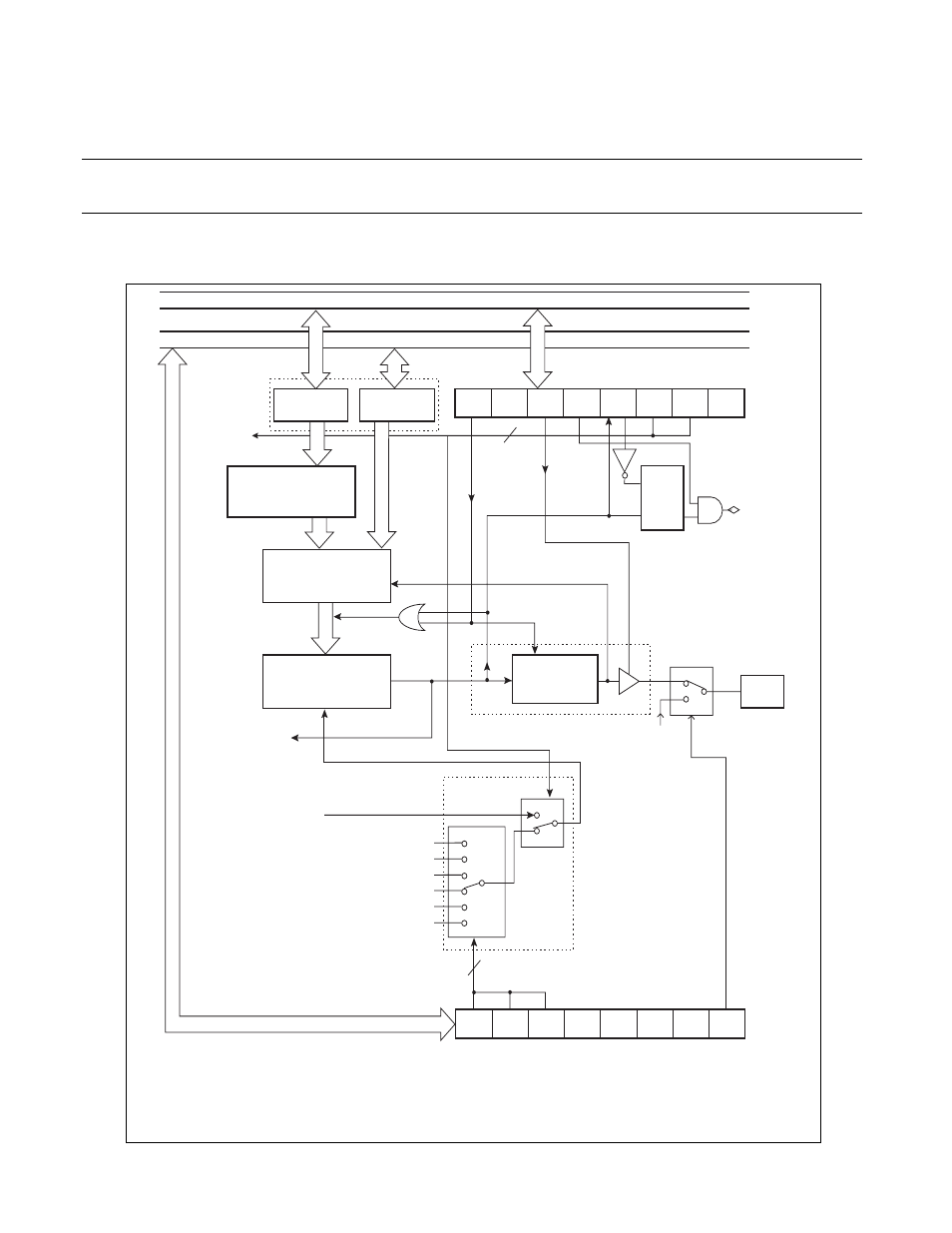

Block Diagram of 8-/16-bit PPG Timer D

The 8-/16-bit PPG timer D consists of the following blocks.

■

Block Diagram of 8-/16-bit PPG Timer D

Figure 16.2-3 Block Diagram of 8-/16-bit PPG Timer D

CLK

MD0

R

S

Q

PEN1

PE1 PIE1 PUF1 MD1 MD0

-

PCS2

PCS0 PCM2 PCM1 PCM0

-

PCS1

3

2

PPGD

REV

High level side data bus

Low level side data bus

PPGD operation mode control register (PPGCD)

PPGD reload

register

Operation

mode control

signal

PRLHD

(High level side)

PRLLD

(Low level side)

Re-

served

PPGD temporary

buffer (PRLBHD)

Interrupt

request

output*

Reload register

L/H selector

Select signal

Clear

Reload

Count start value

Under-

flow

PPGD down counter

(PCNTD)

PPGD underflow

(to PPGC)

Invert

PPGD

output latch

PPG output control circuit

Pin

PPGC

output

PPGC underflow

(from PPGC)

Timebase timer output

(512/HCLK)

Resource clock (1/

φ

)

Resource clock (2/

φ

)

Resource clock (4/

φ

)

Resource clock (8/

φ

)

Resource clock (16/

φ

)

Count

clock

selector

Select signal

PPGC/D count clock select register (PPGCD)

-

: Undefined (from PPG0)

Reservation: Reserved bit

HCLK : Oscillation clock frequency

φ

: Machine clock frequency

*

: The interrupt output of 8-/16- bit PPG timer D is combined to one interrupt by OR circuit with the interrupt

request output of PPG timer C.