FUJITSU F2MCTM-16LX User Manual

Page 585

569

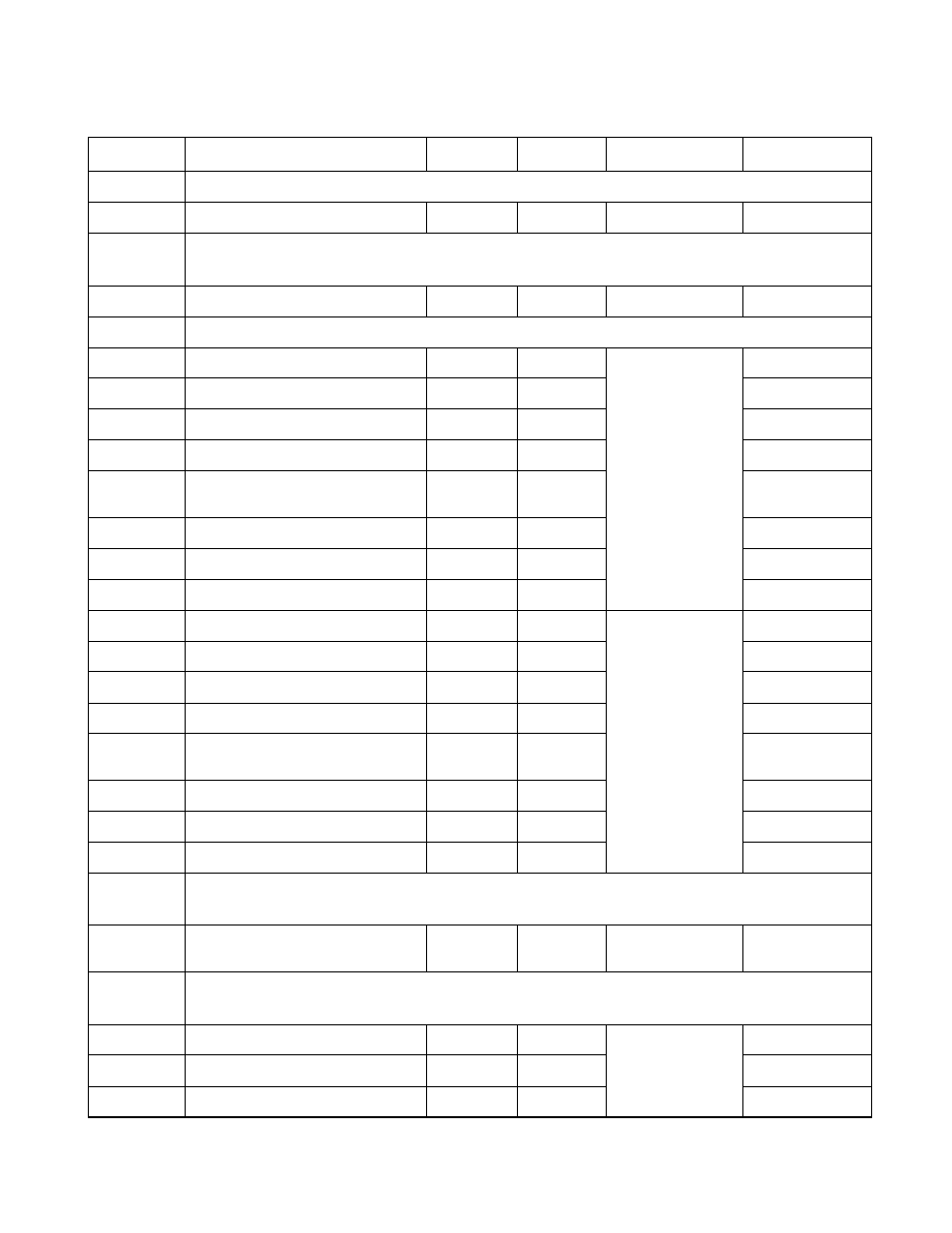

APPENDIX A I/O Maps

000019

H

Reserved

00001A

H

Port A direction register

DDRA

W

Port A

XXX0 0XXX

B

00001B

H

to

00001D

H

Reserved

00001E

H

Port 2 pull-up control register

PUCR2

R/W

Port 2

0 0 0 0 0 0 0 0

B

00001F

H

Reserved

000020

H

Serial mode register 0

SMR0

W, R/W

UART0

0 0 0 0 0 0 0 0

B

000021

H

Serial control register 0

SCR0

W, R/W

0 0 0 0 0 0 0 0

B

000022

H

Reception/transmission data register 0

RDR0/TDR0 R/W

0 0 0 0 0 0 0 0

B

000023

H

Serial status register 0

SSR0

R, R/W

0 0 0 0 1 0 0 0

B

000024

H

Extended communication control

register 0

ECCR0

R, W, R/W

0 0 0 0 0 0 XX

B

000025

H

Extended status control register0

ESCR0

R/W

0 0 0 0 0 1 0 0

B

000026

H

Baud rate generator register 00

BGR00

R/W, R

0 0 0 0 0 0 0 0

B

000027

H

Baud rate generator register 01

BGR01

R/W, R

0 0 0 0 0 0 0 0

B

000028

H

Serial mode register 1

SMR1

W, R/W

UART1

0 0 0 0 0 0 0 0

B

000029

H

Serial control register 1

SCR1

W, R/W

0 0 0 0 0 0 0 0

B

00002A

H

Reception/transmission data register 1

RDR1/TDR1 R/W

0 0 0 0 0 0 0 0

B

00002B

H

Serial status register 1

SSR1

R, R/W

0 0 0 0 1 0 0 0

B

00002C

H

Extended communication control

register1

ECCR1

R, W, R/W

0 0 0 0 0 0 XX

B

00002D

H

Extended status control register 1

ESCR1

R/W

0 0 0 0 0 1 0 0

B

00002E

H

Baud rate generator register 10

BGR10

R/W, R

0 0 0 0 0 0 0 0

B

00002F

H

Baud rate generator register 11

BGR11

R/W, R

0 0 0 0 0 0 0 0

B

000030

H

to

00003A

H

Reserved

00003B

H

Address detection control register 1

PACSR1

R/W

Address Match

Detection 1

0 0 0 0 0 0 0 0

B

00003C

H

to

000047

H

Reserved

000048

H

PPGC operation mode control register

PPGCC

W, R/W

16-bit

PPGC/D

0 X 0 0 0 XX1

B

000049

H

PPGD operation mode control register

PPGCD

W, R/W

0 X 0 0 0 0 0 1

B

00004A

H

PPGC /D count clock selection register

PPGCD

R/W

0 0 0 0 0 0 X 0

B

Table A-1 I/O Map (2/5)

Address

Register

Abbreviation

Access

Peripheral

Initial value