FUJITSU F2MCTM-16LX User Manual

Page 595

579

APPENDIX B Instructions

■

Effective Address Field

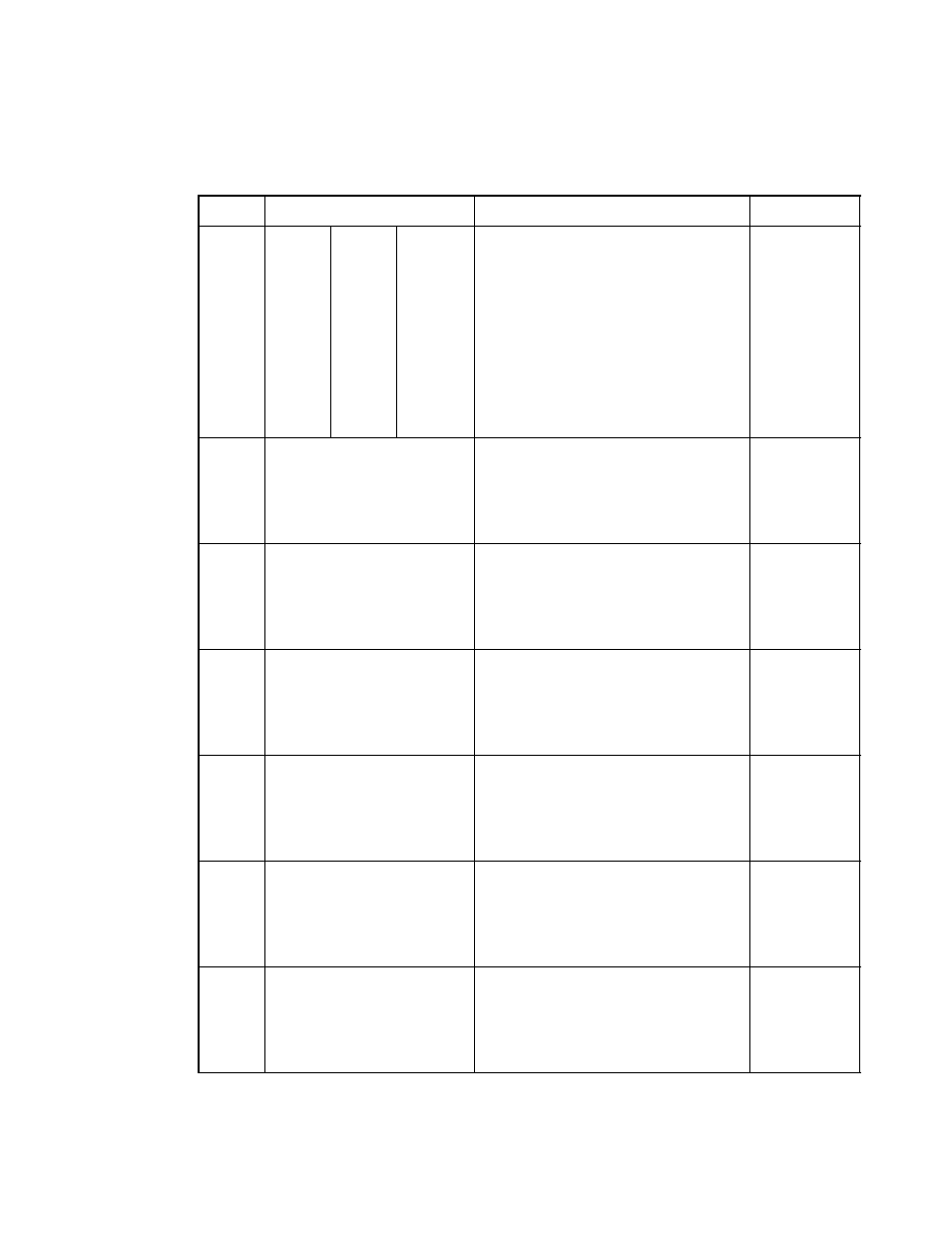

Table B.2-1 lists the address formats specified by the effective address field.

Table B.2-1 Effective Address Field

Code

Representation

Address format

Default bank

00

R0

RW0

RL0

Register direct: Individual parts

correspond to the byte, word, and long

word types in order from the left.

None

01

R1

RW1

(RL0)

02

R2

RW2

RL1

03

R3

RW3

(RL1)

04

R4

RW4

RL2

05

R5

RW5

(RL2)

06

R6

RW6

RL3

07

R7

RW7

(RL3)

08

@RW0

Register indirect

DTB

09

@RW1

DTB

0A

@RW2

ADB

0B

@RW3

SPB

0C

@RW0+

Register indirect with post increment

DTB

0D

@RW1+

DTB

0E

@RW2+

ADB

0F

@RW3+

SPB

10

@RW0+disp8

Register indirect with 8-bit displacement

DTB

11

@RW1+disp8

DTB

12

@RW2+disp8

ADB

13

@RW3+disp8

SPB

14

@RW4+disp8

Register indirect with 8-bit displacement

DTB

15

@RW5+disp8

DTB

16

@RW6+disp8

ADB

17

@RW7+disp8

SPB

18

@RW0+disp16

Register indirect with 16-bit

displacement

DTB

19

@RW1+disp16

DTB

1A

@RW2+disp16

ADB

1B

@RW3+disp16

SPB

1C

@RW0+RW7

Register indirect with index

DTB

1D

@RW1+RW7

Register indirect with index

DTB

1E

@PC+disp16

PC indirect with 16-bit displacement

PCB

1F

addr16

Direct address

DTB

- XG Series P3NK-4452-01ENZD (614 pages)

- FPCAC14C (1 page)

- MCJ3230SS (161 pages)

- MBA3073NC (138 pages)

- T5140 (102 pages)

- T5140 (76 pages)

- MAM3367MC/MP (152 pages)

- MPC3045AH (185 pages)

- MB2142-02 (23 pages)

- MB15F86UL (6 pages)

- MHS2030AT (40 pages)

- MHW2100BS (296 pages)

- MHK2060AT (227 pages)

- Disk Drives MHK2060AT (227 pages)

- MCM3064SS (170 pages)

- Mainboard D1561 (45 pages)

- MHC2040AT (219 pages)

- D1961 (45 pages)

- DISK DRIVES MHM2100AT (231 pages)

- MHR2010AT (250 pages)

- MHZ2120BJ (320 pages)

- MCE3064AP (175 pages)

- LQFP-64P (16 pages)

- Solaris PCI GigabitEthernet 3.0 (115 pages)

- MAY2036RC (94 pages)

- MAB3091 (142 pages)

- MPE3XXXAT (191 pages)

- MHV2040AH (40 pages)

- MHW2040AC (278 pages)

- ETERNUSmgr P2X0-0202-01EN (64 pages)

- VSS Hardware Provider 2.1 (134 pages)

- MAG3182FC (61 pages)

- MAU3147NC/NP (130 pages)

- MAX3147RC (94 pages)

- MHV2160BT (296 pages)

- MHV2040AT (280 pages)

- MAW3300NC/NP (130 pages)

- DeskPower E623 (50 pages)

- MAG3182LC (133 pages)

- OPTICAL DISK DRIVES MDG3064UB (42 pages)

- MHF2021AT (225 pages)

- MHR2040AT (40 pages)

- Single Drive FTM7926FB (1 page)

- PG-FCS103 (98 pages)

- MAS3735FC (114 pages)