FUJITSU F2MCTM-16LX User Manual

Page 590

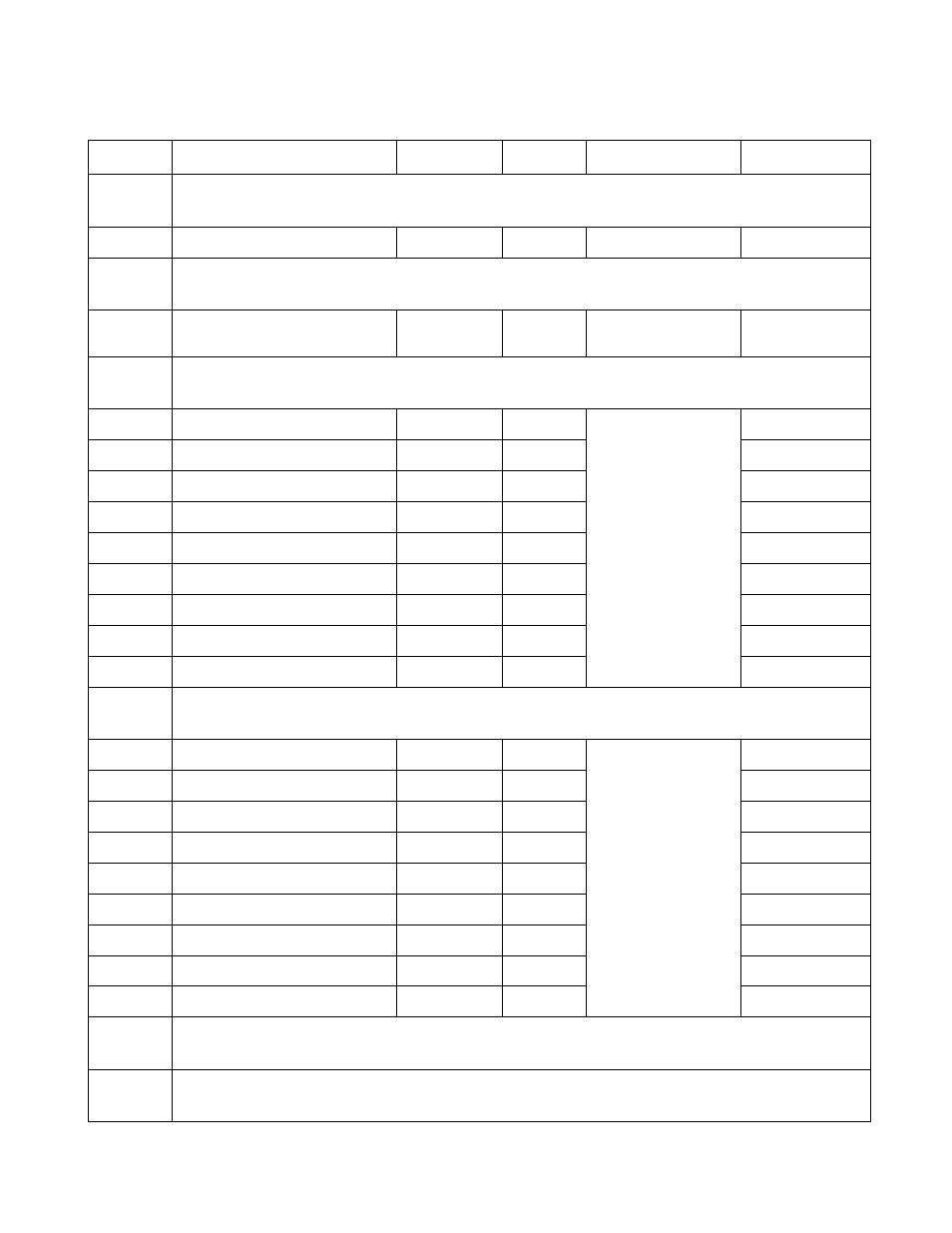

574

APPENDIX

7950

H

to

795F

H

Reserved

7960

H

Clock supervisor control register

CSVCR

R, R/W

Clock supervisor

0 0 0 1 1 1 0 0

B

7961

H

to

796D

H

Reserved

796E

H

CAN direct mode register

(For only MB90V340)

CDMR

R/W

CAN Clock Sync

XXXXXXX0B

796F

H

to

79DF

H

Reserved

79E0

H

Detection address setting 0

PADR0

R/W

Address Match

Detection 0

XXXXXXXX

B

79E1

H

Detection address setting 0

PADR0

R/W

XXXXXXXX

B

79E2

H

Detection address setting 0

PADR0

R/W

XXXXXXXX

B

79E3

H

Detection address setting 1

PADR1

R/W

XXXXXXXX

B

79E4

H

Detection address setting 1

PADR1

R/W

XXXXXXXX

B

79E5

H

Detection address setting 1

PADR1

R/W

XXXXXXXX

B

79E6

H

Detection address setting 2

PADR2

R/W

XXXXXXXX

B

79E7

H

Detection address setting 2

PADR2

R/W

XXXXXXXX

B

79E8

H

Detection address setting 2

PADR2

R/W

XXXXXXXX

B

79E9

H

to

79EF

H

Reserved

79F0

H

Detection address setting 3

PADR3

R/W

Address Match

Detection 1

XXXXXXXX

B

79F1

H

Detection address setting 3

PADR3

R/W

XXXXXXXX

B

79F2

H

Detection address setting 3

PADR3

R/W

XXXXXXXX

B

79F3

H

Detection address setting 4

PADR4

R/W

XXXXXXXX

B

79F4

H

Detection address setting 4

PADR4

R/W

XXXXXXXX

B

79F5

H

Detection address setting 4

PADR4

R/W

XXXXXXXX

B

79F6

H

Detection address setting 5

PADR5

R/W

XXXXXXXX

B

79F7

H

Detection address setting 5

PADR5

R/W

XXXXXXXX

B

79F8

H

Detection address setting 5

PADR5

R/W

XXXXXXXX

B

79F9

H

to

7BFF

H

Reserved

7C00

H

to

7CFF

H

Reserved for CAN interface 1. (For more information, see Table 21.3-1 .)

Table A-2 I/O Map (7900

H

- 7FFF

H

) (2/3)

Address

Register

Abbreviation

Access

Peripheral

Initial value