FUJITSU F2MCTM-16LX User Manual

Page 220

204

CHAPTER 12 WATCHDOG TIMER

12.4

Explanation of Operations of Watchdog Timer Functions

After starting, when the watchdog timer reaches the set interval time without the

counter being cleared, a watchdog reset occurs.

■

Operations of Watchdog Timer

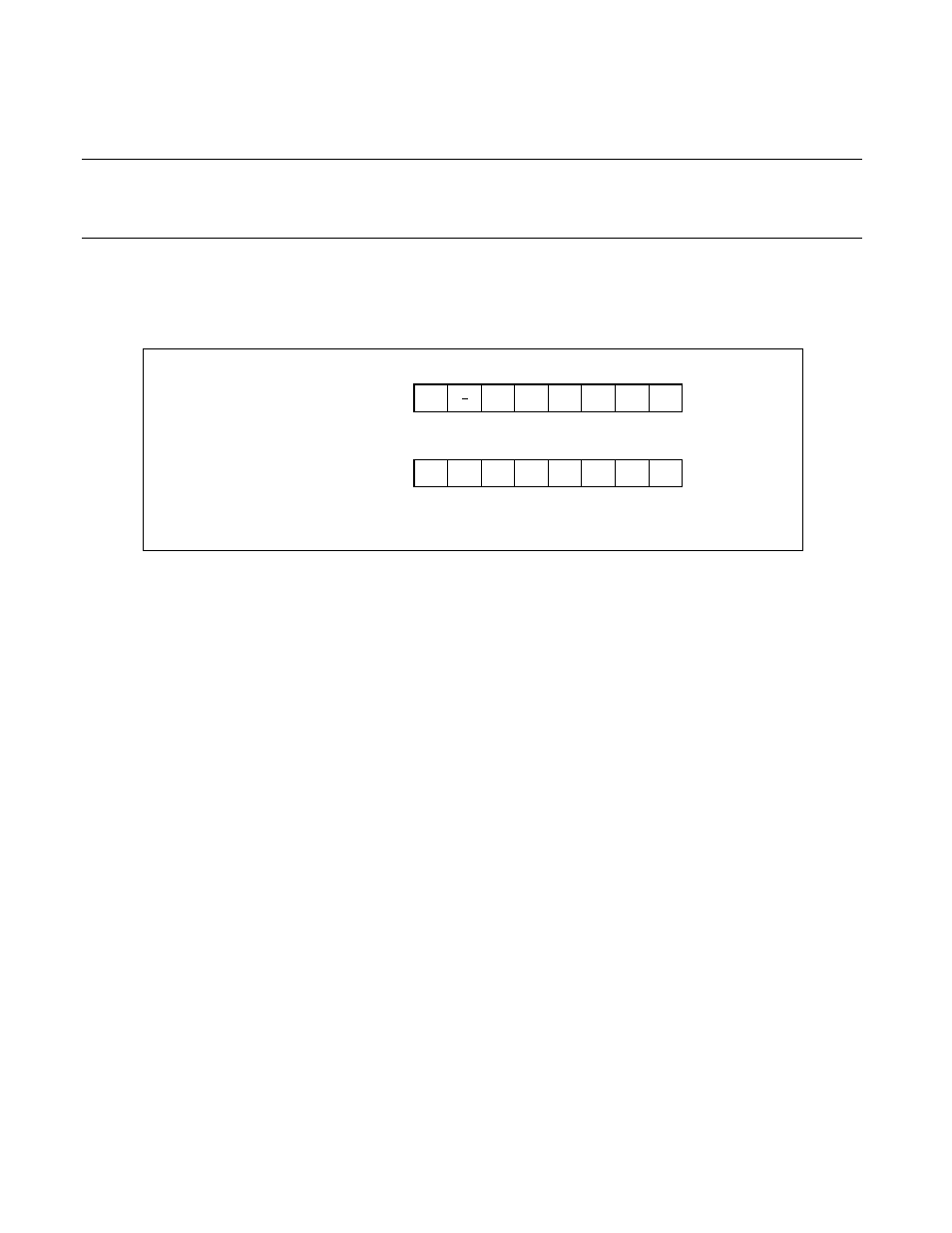

The operation of the watchdog timer requires the settings shown in Figure 12.4-1 .

Figure 12.4-1 Setting of Watchdog Timer

●

Selecting clock input source

•

The timebase timer or watch timer can be selected as the clock input source of the count clock to the

watchdog timer. When the watchdog clock select bit (WTC: WDCS) is set to "1", the timebase timer is

selected. When the bit is set to 0, the watch timer is selected. After a reset, the bit returns to "1".

•

During operation in the sub clock mode, set the WDCS bit to 0 to select the watch timer.

●

Setting interval time

•

Set the interval time select bits (WDTS: WT1, WT0) to select the interval time for the watchdog timer.

•

Set the interval time concurrently when starting the watchdog timer. Writing to the bit is ignored after the

watchdog timer is started.

●

Activating watchdog timer

When "0" is written to the watchdog timer control bit (WDTC: WTE) after a reset, the watchdog timer is

started and starts incrementing.

ERST SRST

WT1 WT0

WTE

PONR

WRST

0

bit7

6

5

4

3

2

1

bit0

WTOF WTR

WTC1 WTC0

WTC2

WDCS SCE WTIE

bit7

6

5

4

3

2

1

bit0

Watchdog timer control register

(WDTC)

❍

: Used bit

0 : Set to "0".

Watch timer control register

(WTC)

❍

❍

❍