1 data polling flag (dq7), Data polling flag (dq7) – FUJITSU F2MCTM-16LX User Manual

Page 557

541

CHAPTER 24 512K-BIT FLASH MEMORY

24.6.1

Data Polling Flag (DQ7)

The data polling flag (DQ7) uses the data polling function to post that the automatic

algorithm is being executed or has terminated

■

Data Polling Flag (DQ7)

Table 24.6-3 and Table 24.6-4 list the state transitions of the data polling flag.

●

Write

Read-access during execution of the automatic write algorithm causes the flash memory to output the

opposite data of bit 7 last written, regardless of the value at the address specified by the address signal.

Read-access at the end of the automatic write algorithm causes the flash memory to output bit 7 of the read

value of the address specified by the address signal.

●

Chip erase

Read-access during execution of the chip erase algorithm causes the flash memory to output 0. Read-access

at the end of the automatic chip algorithm causes the flash memory to output 1 in the same way.

Note:

When the automatic algorithm is being started, read-access to the specified address is ignored. Since

termination of the data polling flag (DQ7) can be accepted for a data read and other bits output, data

read after the automatic algorithm has terminated should be performed after read-access has confirmed

that data polling has terminated.

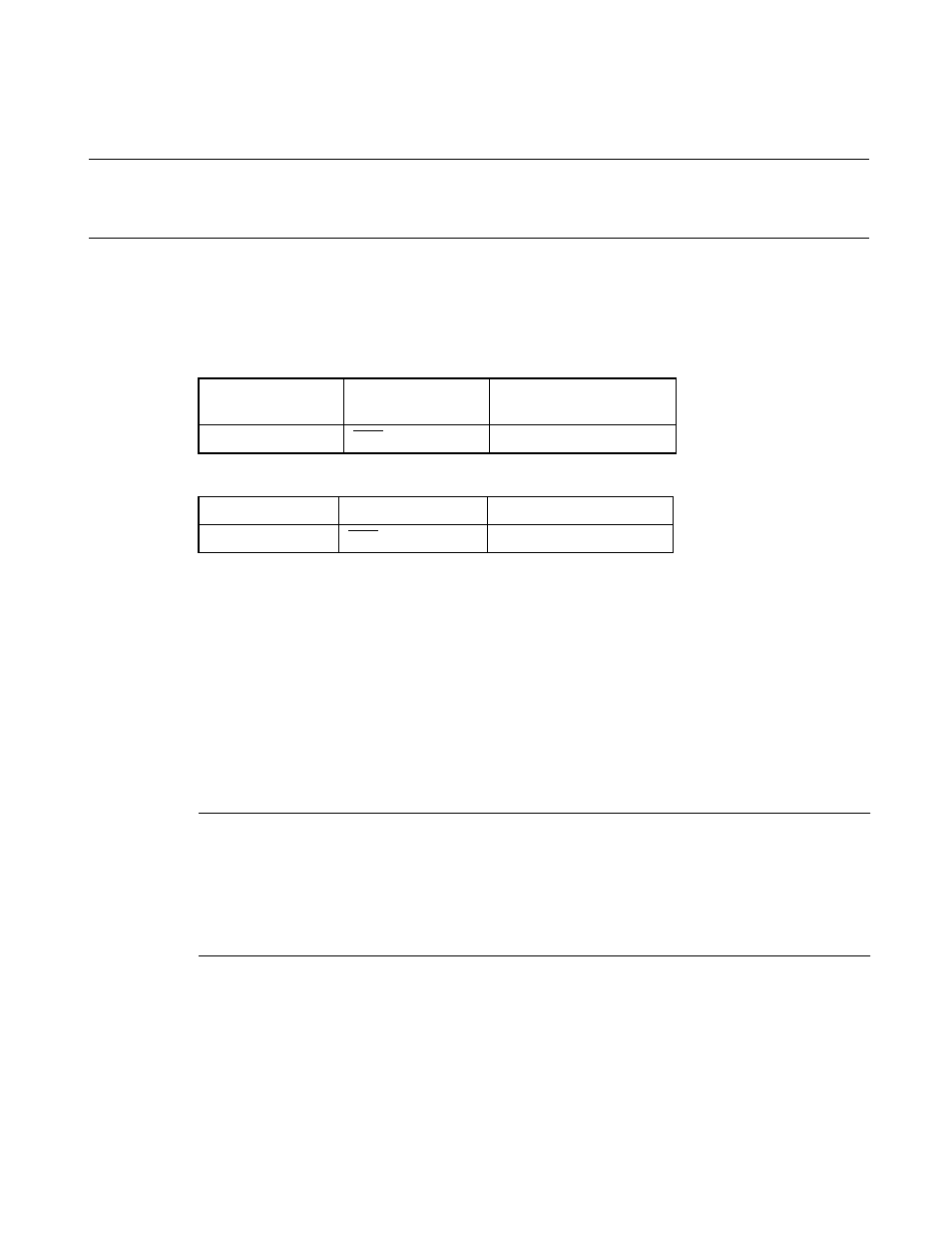

Table 24.6-3 State Transition of Data Polling Flag (State change at normal operation)

Operating State

Programming

→ Completed

Chip Erasing

→

Completed

DQ7 DQ7

→ DATA:7

0

→ 1

Table 24.6-4 State Transition of Data Polling Flag (State change at abnormal operation)

Operating State

Programming

Chip Erasing

DQ7 DQ7 0