FUJITSU F2MCTM-16LX User Manual

Page 605

589

APPENDIX B Instructions

●

Program counter relative branch addressing (rel)

The address of the branch destination is a value determined by adding an 8-bit offset to the program

counter (PC) value. If the result of addition exceeds 16 bits, bank register incrementing or decrementing is

not performed and the excess part is ignored, and therefore the address is contained within a 64-Kbyte

bank. This addressing is used for both conditional and unconditional branch instructions. Address bits 16 to

23 are indicated by the program bank register (PCB).

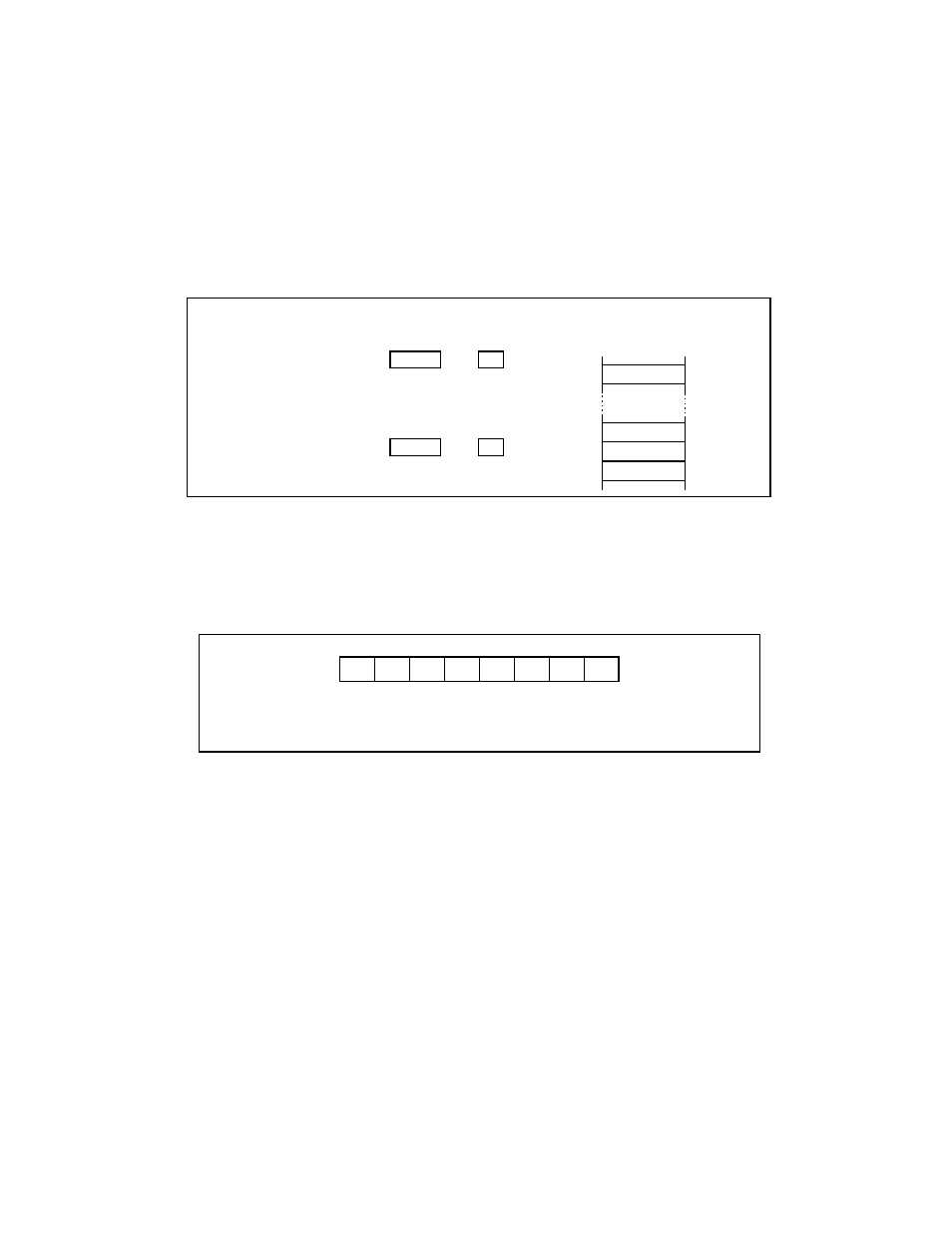

Figure B.4-7 Example of Program Counter Relative Branch Addressing (rel)

●

Register list (rlst)

Specify a register to be pushed onto or popped from a stack.

Figure B.4-8 Configuration of the Register List

BRA 3B20

H

3 C 2 0

PC

4 F

PCB

3 B 2 0

PC

4 F

PCB

Before execution

After execution

Memory space

(This instruction causes an unconditional relative branch.)

Next instruction

4F3B20

H

4F3C20

H

6 0

F E

4F3C21

H

BRA 3B20

H

F F

4F3C22

H

RW7 RW6 RW5 RW4 RW3 RW2 RW1 RW0

MSB

LSB

A register is selected when the corresponding bit is 1 and deselected when the bit is 0.

: Highest bit

MSB

: Lowest bit

LSB