FUJITSU F2MCTM-16LX User Manual

Page 361

345

CHAPTER 18 8-/10-BIT A/D CONVERTER

■

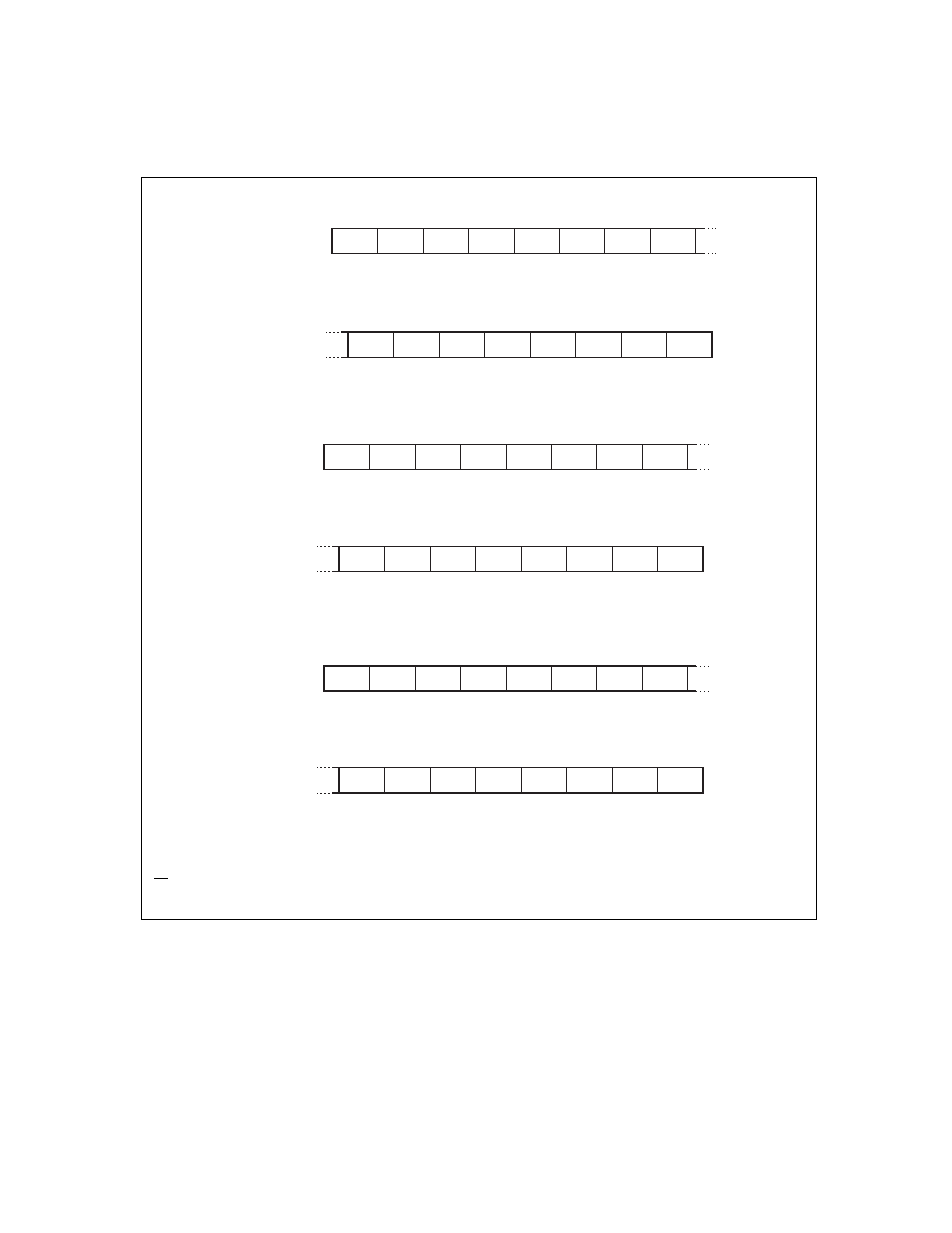

List of Registers and Reset Values of 8-/10-bit A/D Converter

Figure 18.3-1 List of Register and Reset Value of 8-/10-bit A/D Converter

■

Generation of Interrupt from 8-/10-bit A/D Converter

In the 8-/10-bit A/D converter, when the A/D conversion results are stored in the A/D data register

(ADCR0, 1), the interrupt request flag bit in the A/D control status register (ADCS1:INT) is set to "1".

When an interrupt request is enabled (ADCS1:INTE = 1), an interrupt is generated.

A/D control status register (High)

15

14

13

12

11

10

9

8

Address

:000069

H

BUSY INT

INTE PAUS STS1 STS0 STRT

−

ADCS1

R/W

R/W

R/W

R/W

R/W

R/W

W

7

5

4

3

2

1

0

MD1 MD0

S10

ADCS0

R/W

R/W

R/W

R/W

ANS2 ANS1 ANS0

ANE2 ANE1

ANE3

ANE0

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

6

Address

:000068

H

−

A/D control status register (Low)

Data register (High)

15

14

13

12

11

10

9

8

Address

:00006B

H

−

−

−

−

−

D9

D8

ADCR1

7

6

5

4

3

2

1

0

Address

:00006A

H

D7

D6

D5

D4

D3

D2

D1

D0

ADCR0

R

R

R

R

R

R

R

R

−

−

−

−

−

−

−

−

−

−

−

−

−

−

R

R

−

A/D setting register (High)

15

14

13

12

11

10

9

8

Address

:00006D

H

ST2

ST1

ST0

CT1

CT2

CT0

ANS3

ADSR1

A/D setting register (Low)

7

6

5

4

3

2

1

0

Address

:00006C

H

ADSR0

00000000

B

00000000

B

00000000

B

XXXXXX00

B

000XXXX0

B

0000000X

B

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

X

W

R/W

R

Reset value

Reset value

Reset value

Reset value

Reset value

Reset value

: Read/Write

: Read only

: Write only

: Undefined bit

: Indeterminate

Reserved

Reserved

Data register (Low)

Reserved