FUJITSU F2MCTM-16LX User Manual

Page 309

293

CHAPTER 16 8-/16-BIT PPG TIMER

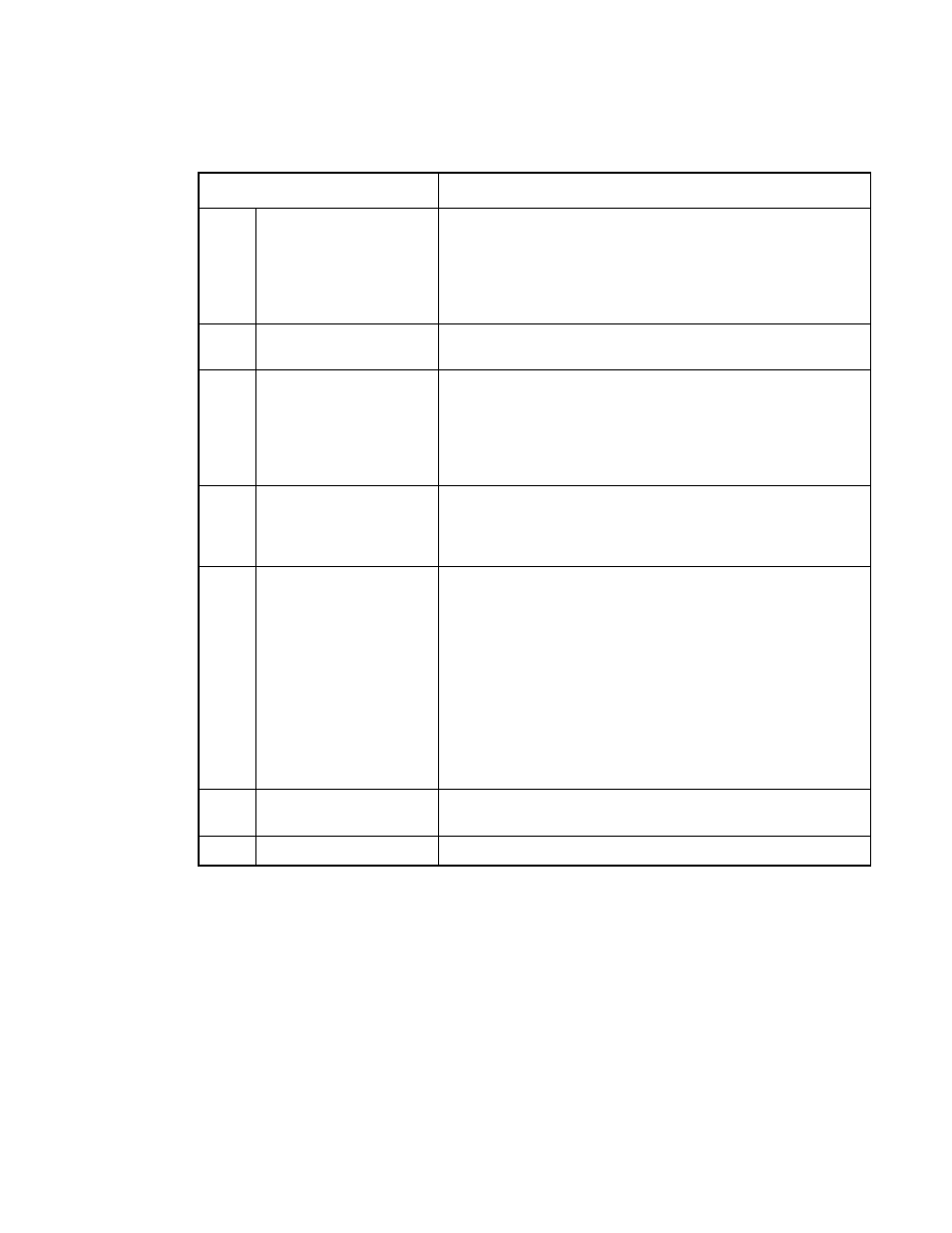

Table 16.3-2 Functions of PPGC Operation Mode Control Register (PPGCC)

Bit Name

Function

bit7

PEN0:

PPG0 operation enable bit

This bit enables or disables the count operation of the 8-/16-bit PPG timer

C.

When set to "0": Count operation disabled

When set to "1": Count operation enabled

• When the count operation is disabled (PEN0=0), and the pulse output

is enabled (PE0=1), the output is held at a Low level.

bit6

Undefined bit

Read: The value is undefined.

Write: No effect

bit5

PE0:

PPG0 pin output enable bit

This bit switches between PPGC pin functions and enables or disables the

pulse output.

When set to "0": PPGC pin functions as general-purpose I/O port. The

pulse output is disabled.

When set to "1": PPGC pin functions as PPGC output pin. The pulse

output is enabled.

bit4

PIE0:

Underflow interrupt enable

bit

This bit enables or disables an interrupt.

When set to "0": No interrupt request generated even at underflow

(PUF0 = 1).

When set to "1": Interrupt request generated at underflow (PUF0 = 1)

bit3

PUF0:

Underflow generation flag

bit

8-bit PPG output 2-channel independent operation mode, 8+8-bit

PPG output operation mode:

When the value of the PPGC down counter is decremented from

"00

H

" to"FF

H

", an underflow occurs (PUF0 = 1).

16-bit PPG output operation mode:

When the values of the PPGC and PPGD down counters are decremented

from "0000

H

" to "FFFF

H

", an underflow occurs (PUF0 = 1).

• When an underflow occurs (PUF0 = 1) with an underflow interrupt

enabled (PIE0 = 1), an interrupt request is generated.

When set to "0": Clears counter

When set to "1": No effect

Read by read modify write instructions: 1 is read.

bit2

bit1

Undefined bits

Write: No effect

Read: The value is undefined.

bit0

Reserved: Reserved bit

Always set this bit to 1.