FUJITSU F2MCTM-16LX User Manual

Page 156

140

CHAPTER 8 LOW-POWER CONSUMPTION MODE

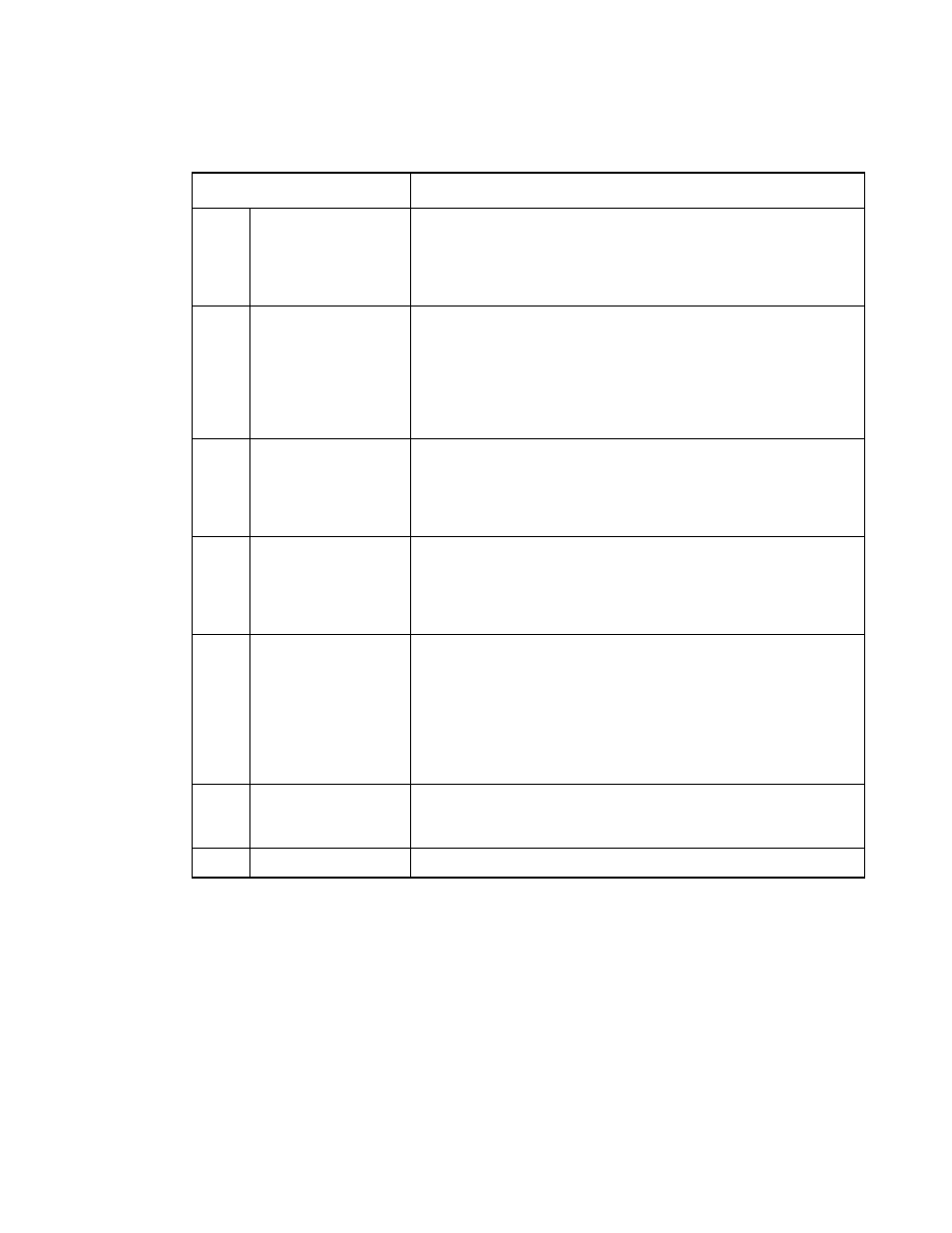

Table 8.3-1 Functions of Low-power Consumption Mode Control Register (LPMCR)

Bit name

Function

bit7

STP:

Stop mode bit

This bit transits to the stop mode.

When the bit is set to "0": No effect.

When the bit is set to "1": The CPU enters the stop mode.

Read: "0" is always read.

•

The bit is initialized to "0" when a reset or external interrupt occurs.

bit6

SLP:

Sleep mode bit

This bit shift to sleep mode

When the bit is set to "0": No effect.

When the bit is set to "1": The CPU enters the sleep mode.

Read: "0" is always read.

•

The bit is initialized to "0" when a reset or external interrupt occurs.

•

When the STP and SLP bits are set to "1" at the same time, the STP bit

supersedes the SLP bit, causing a transition to stop mode.

bit5

SPL:

Pin state specification bit

The bit is used to set the state of input/output pins after transition to the stop

mode, watch mode, or timebase timer mode.

When the bit is set to "0": The current level of input/output pins is held.

When the bit is set to "1": The I/O pins enter a high impedance state.

•

The bit is initialized to "0" at a reset.

bit4

RST:

Internal reset signal

generation bit

This bit generates software reset.

When the bit is set to "0": An internal reset signal for three machine cycles

is generated.

When the bit is set to "1": No effect

Read: "1" is always read.

bit3

TMD:

Watch mode bit

This bit shift to watch mode or timebase timer mode

When the bit is set to "0": If the main clock mode or PLL clock mode is

used, the bit transits to the timebase timer mode.

If the sub-clock mode is used, the bit transits to

the watch mode.

When the bit is set to "1": No effect

•

The bit is set to "1" when a reset or interrupt occurs.

Read: "1" is always read.

bit1

bit2

CG1, CG0:

CPU suspended cycle

number select bits

These bits are used to set the halt cycle count of the CPU clock in the CPU

intermittent operation mode.

•

Any reset causes the bit to return to the reset value.

bit0

Reserved: reserved bit

Always set this bit to "0".