FUJITSU F2MCTM-16LX User Manual

Page 155

139

CHAPTER 8 LOW-POWER CONSUMPTION MODE

8.3

Low-Power Consumption Mode Control Register (LPMCR)

This register switches to or releases the low-power consumption mode. This register

also generates the internal reset signal and sets the halt cycle count during the CPU

intermittent operation mode.

■

Low-Power Consumption Mode Control Register (LPMCR)

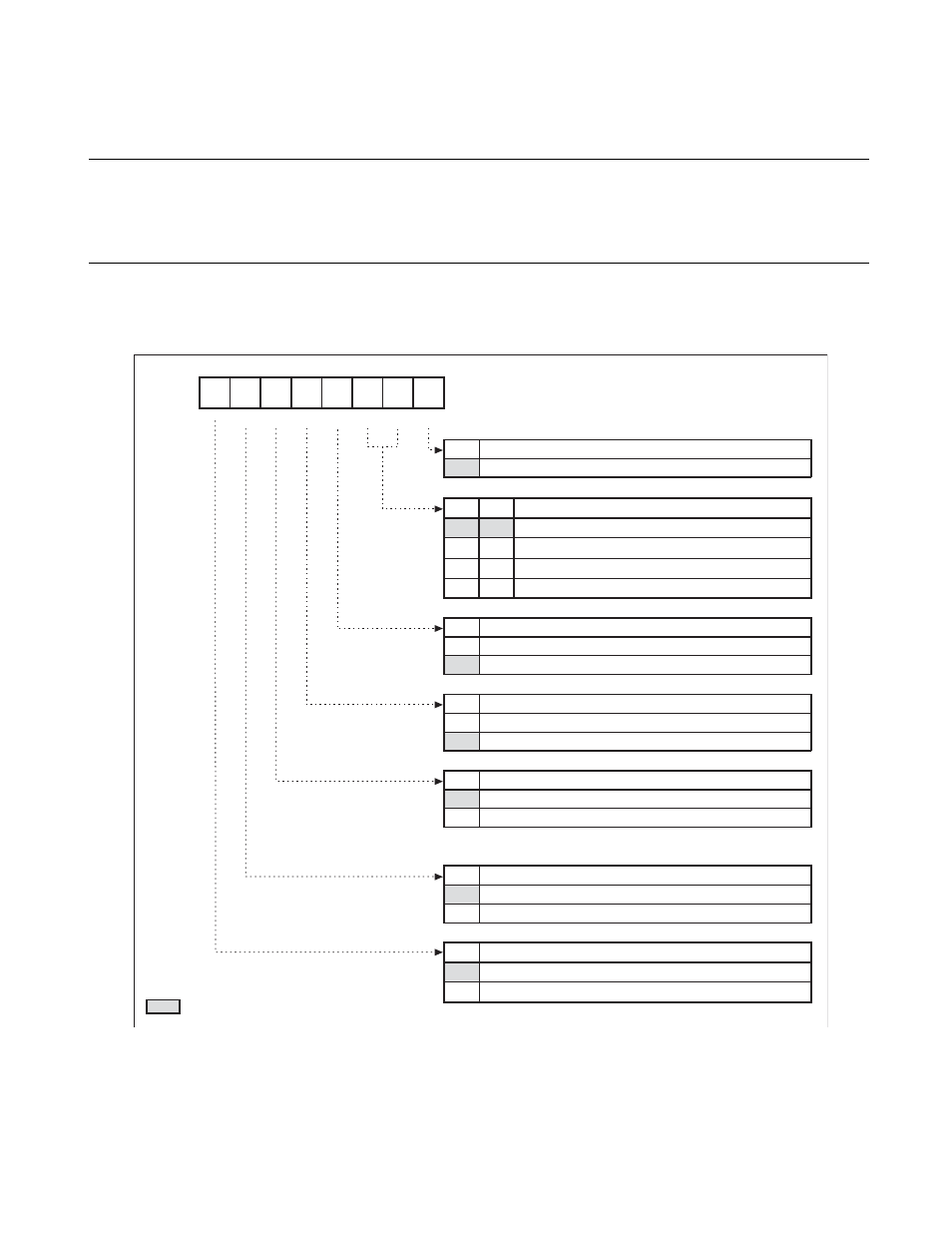

Figure 8.3-1 Configuration of the Low-power Consumption Mode Control Register (LPMCR)

0

0 0 0 1 1 0 0 0

B

4

5

3

2

1

0

bit0

6

7

: Reset value

: Read/Write

R/W

: Write only

W

TMD

0

1

bit3

RST

0

1

bit4

SPL

0

1

Valid only in timebase timer, watch and stop mode

bit5

0

1

STP

bit7

bit6

SLP

0

1

R/W

R/W

R/W

W

W

R/W

W

W

bit2

bit1

CG1 CG0

0

0

1

1

0

1

0

1

STP SLP SPL RST TMD CG1 CG0

Re-

served

Reset value

Reserved bit

Be sure to set this bit to 0.

Re-

served

CPU suspended cycle number select bit

0 cycle (CPU clock = peripheral clock)

8 cycle (CPU clock: peripheral clock = 1: approx. 3 to 4)

16 cycle (CPU clock: peripheral clock = 1: approx. 5 to 6)

32 cycle (CPU clock: peripheral clock = 1: approx. 9 to 10)

Watch mode bit

Transfer to watch mode or timebase timer

No effect

Internal reset signal generation bit

Generate the internal reset signal of 3-machine cycle

No effect

Pin state specification bit

Hold I/O pin state

High-Z

Sleep mode bit

No effect

Change to sleep mode

Stop mode

No effect

Change to stop mode

Address

0000A0H