3 16-bit timer registers (tmr), Bit timer registers (tmr) – FUJITSU F2MCTM-16LX User Manual

Page 265

249

CHAPTER 14 16-BIT RELOAD TIMER

14.3.3

16-bit Timer Registers (TMR)

The 16-bit timer registers are 16-bit down counters. At read, the value being counted is

read.

■

16-bit Timer Registers (TMR)

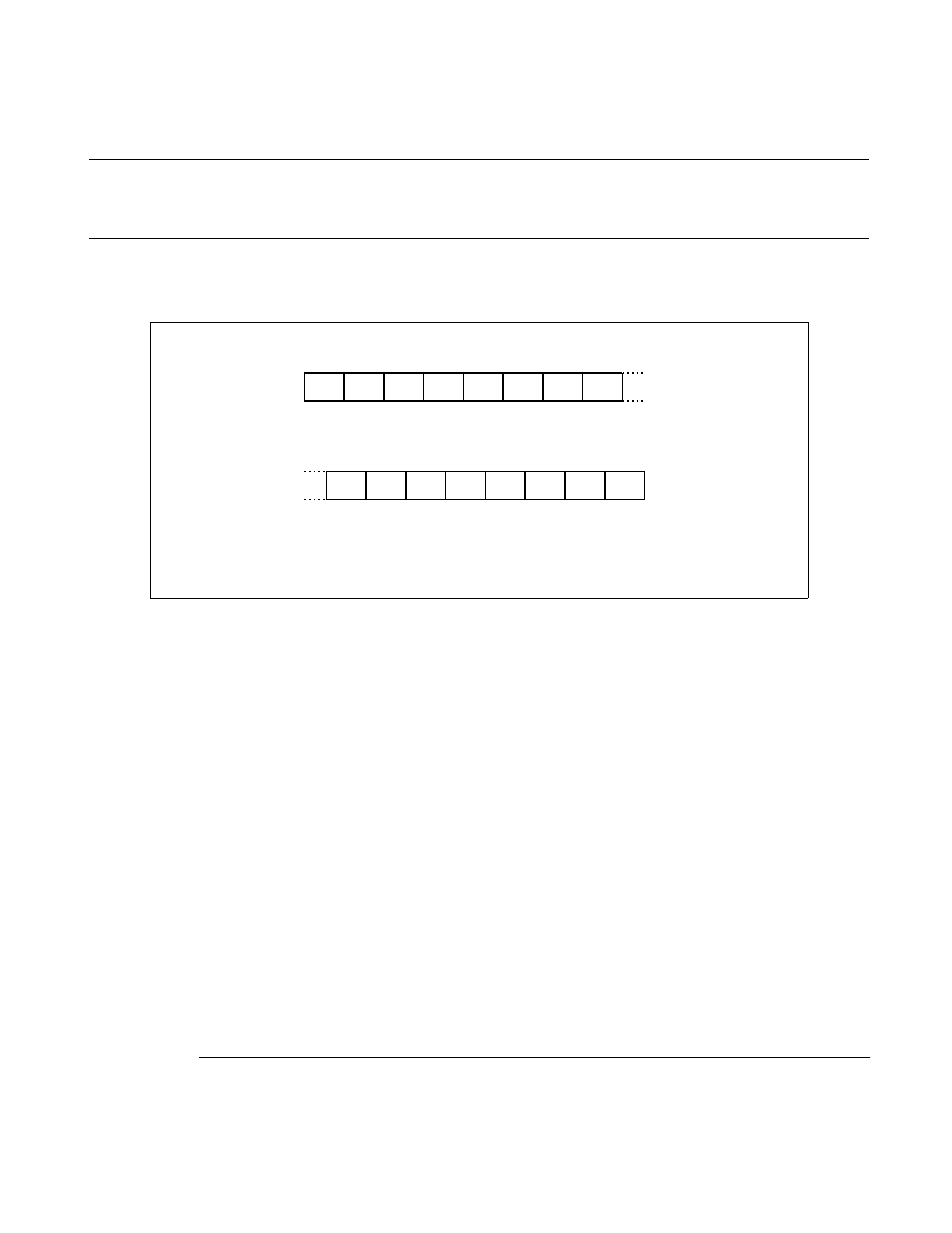

Figure 14.3-5 16-bit Timer Registers (TMR)

When the timer operation is enabled (TMCSR:CNTE = 1) and the start trigger is inputted, the value set in

the 16-bit reload register (TMRLR) is reloaded to the 16-bit timer register (TMR), starting the TMR count

operation.

When the timer operation is disabled (TMCSR:CNTE = 0), the TMR value is retained.

When the TMR value is counted down from "0000

H

" to "FFFF

H

" during the TMR count operation, an

underflow occurs.

[Reload mode]

When the TMR underflows, the value set in the TMRLR is reloaded to the TMR, restarting the TMR count

operation.

[One-shot mode]

When the TMR underflows, the TMR count operation is stopped, entering the start trigger input wait state.

The TMR value is retained to "FFFF

H

".

Notes:

•

The TMR can be read during the TMR count operation. However, always use the word instruction

(MOVW).

•

The TMR and the TMRLR are assigned to the same address. At write, the set value can be written to the

TMRLR without affecting the TMR. At read, the TMR value being counted can be read.

R

R

R

R

R

R

R

R

D11

D8

D9

D10

D15

D12

D13

D14

R

R

R

R

R

R

R

R

D3

D0

D1

D2

D7

D4

D5

D6

15

14

13

12

11

10

9

8

XXXXXXXX

B

XXXXXXXX

B

7

6

5

4

3

2

1

0

TMR2 : 00794D

H

TMR3 : 00794F

H

TMR2 : 00794C

H

TMR3 : 00794E

H

Address:

Reset value

Address:

Reset value

R

: Read only

X

: Undefined