3 clock supervisor control register (csvcr), Clock supervisor control register (csvcr), 113 chapter 6 clock supervisor – FUJITSU F2MCTM-16LX User Manual

Page 129

113

CHAPTER 6 CLOCK SUPERVISOR

6.3

Clock Supervisor Control Register (CSVCR)

This register switches main clock/sub clock/PLL clock, and selects the oscillation

stabilization wait time and PLL clock multiplication rate.

■

Clock Supervisor Control Register (CSVCR)

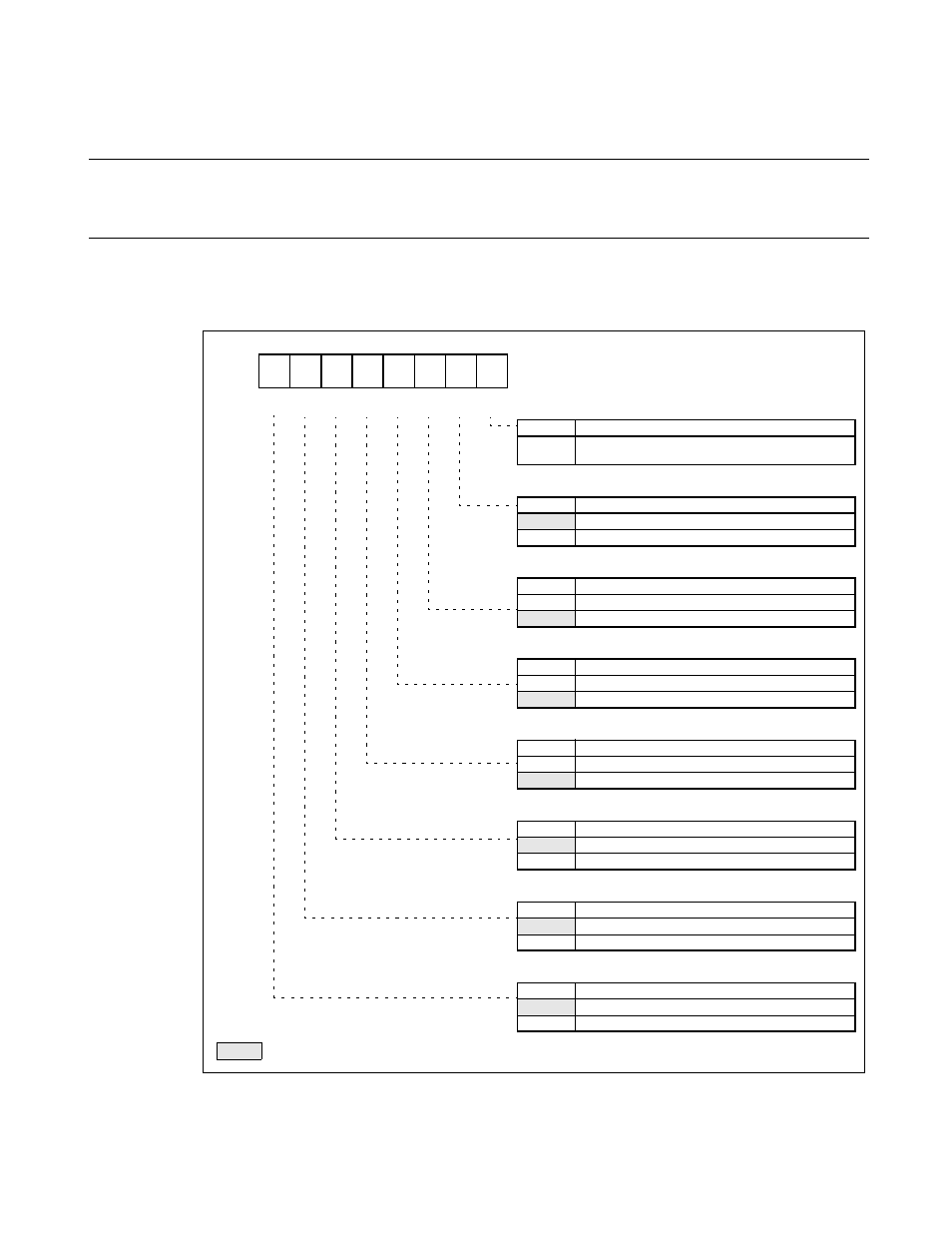

Figure 6.3-1 Clock Supervisor Control Register (CSVCR)

7

6

5

4

3

2

1

0

B

R/W

R

R

R/W

R/W

R/W

R/W R/W

bit0

Reserved

Reserved bit

0

Be sure to write "0" to this bit.

Read value is always "0".

bit1

SRST

Sub-clock mode reset

0

No generating reset on subclock mode transition

1

Generating reset on subclock mode transition

bit2

SSVE

Sub clock supervisor enable

0

Sub clock supervisor is disabled.

1

Sub clock supervisor is enabled.

bit3

MSVE

Main clock supervisor enable

0

Main clock supervisor is disabled.

1

Main clock supervisor is enabled.

bit4

RCE

CR oscillation clock enable

0

CR oscillation clock is stopped.

1

CR oscillation clock is enabled.

bit5

SM

Sub clock missing

0

Missing sub-clock has not been detected.

1

Missing sub-clock has been detected.

bit6

MM

Main clock missing

0

Missing main clock has not been detected.

1

Missing main clock has been detected.

bit7

SCKS

Sub clock select (for "S" suffix product)

0

Not use the CR oscillation clock as sub clock

1

Use the CR oscillation clock as sub clock

R/W

:

Read/Write

R

:

Read only

:

Reset value

0 0 0 1 1 1 0 0

Rese-

SCKS MM

SM RCE MSVE SSVE SRST

Initial value

H

007960

rved

Address