2 a/d control status register (low) (adcs0), A/d control status register (low) (adcs0) – FUJITSU F2MCTM-16LX User Manual

Page 365

349

CHAPTER 18 8-/10-BIT A/D CONVERTER

18.3.2

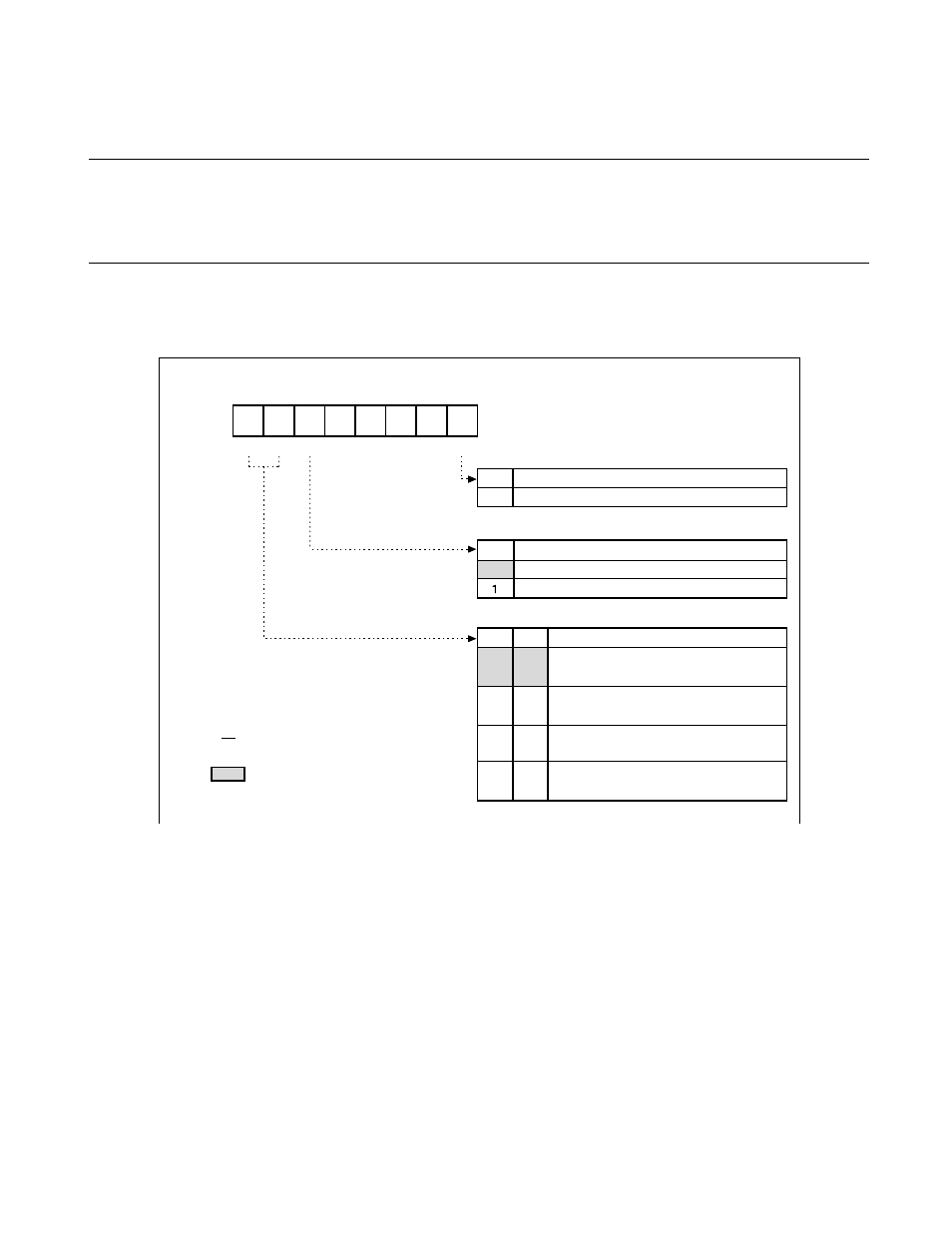

A/D Control Status Register (Low) (ADCS0)

The A/D control status register (Low) (ADCS0) provides the following settings:

• Selecting A/D conversion mode

• Selecting start channel and end channel of A/D conversion

■

A/D Control Status Register (Low) (ADCS0)

Figure 18.3-3 A/D Control Status Register (Low) (ADCS0)

Reset value

Address

000XXXX0

B

4

5

3

2

1

0

6

7

X

R/W

R/W

R/W

R/W

Reserved bit

bit0

Resolution select bit

bit5

MD1

0

0

1

1

A/D conversion mode select bit

bit7

MD0

0

1

0

1

bit6

Single-shot conversion mode 1

(restartable during conversion)

Single-shot conversion mode 2

(not-restartable during conversion)

Continuous conversion mode

(not-restartable during conversion)

Pause-conversion mode

(not-restartable during conversion)

S10

0

MD1 MD0 S10

Re-

served

-

-

-

-

-

-

-

-

Reserved

0

000068

H

Resolution of A/D conversion is set to 10-bit.

Resolution of A/D conversion is set to 8-bit.

Always write 0.

R/W

: Read/Write

: Reset value

: Undefined bit

: Indeterminate