1 accumulator (a), Accumulator (a), 40 chapter 2 cpu – FUJITSU F2MCTM-16LX User Manual

Page 56

40

CHAPTER 2 CPU

2.7.1

Accumulator (A)

The accumulator (A) register consists of 2 16-bit arithmetic operation registers (AH and

AL), and is used as a temporary storage for operation results and transfer data.

■

Accumulator (A)

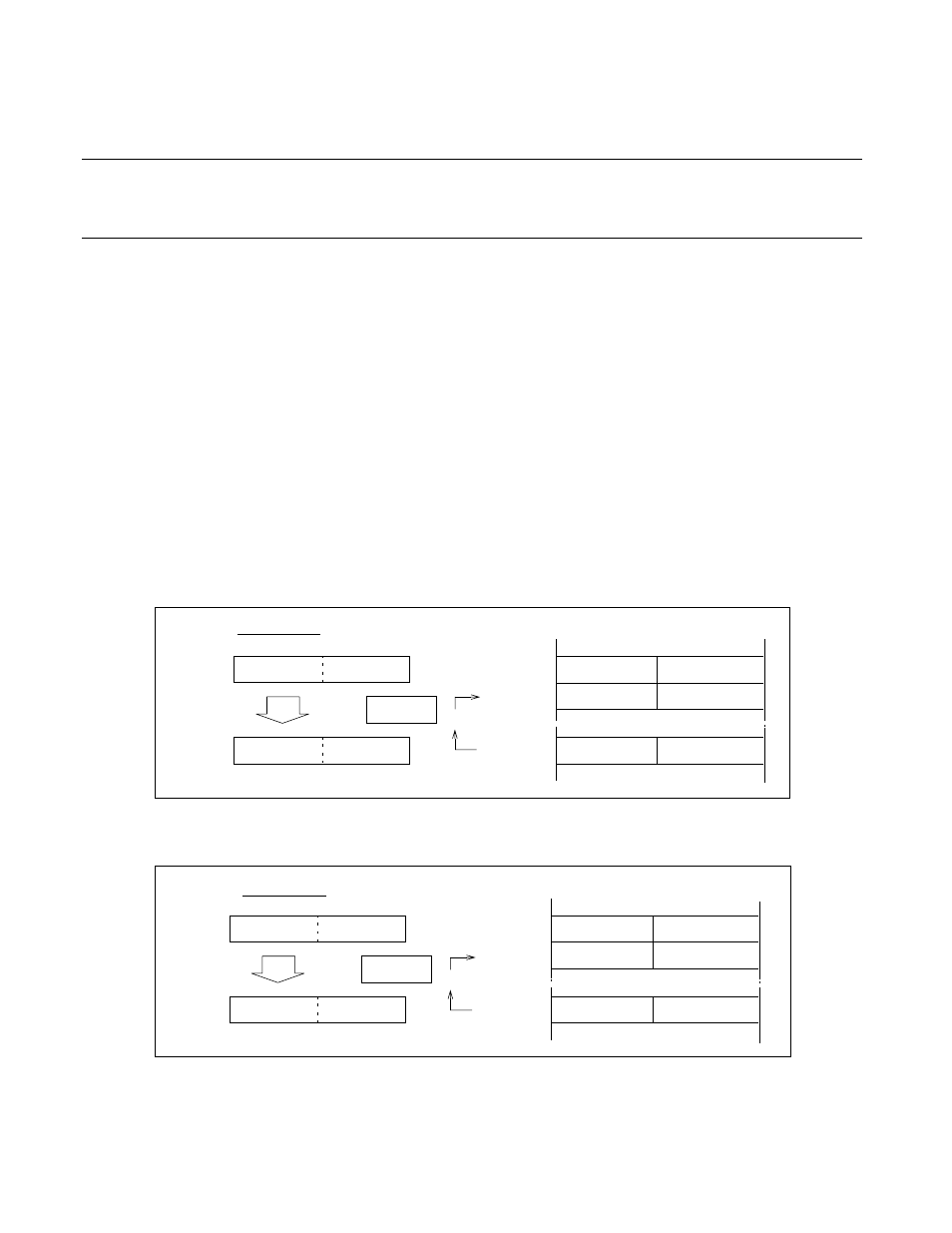

During 32-bit data processing, AH and AL are used together. Only AL is used for word processing in 16-

bit data processing mode or for byte processing in 8-bit data processing mode (see Figure 2.7-3 and Figure

2.7-4 ). The data stored in the A register can be operated upon with the data in memory or registers (Ri,

Rwi, or RLi). In the same manner as with the F

2

MC-8L, when a word or shorter data item is transferred to

AL, the previous data item in AL is automatically sent to AH (data preservation function). The data

preservation function and operation between AL and AH help improve processing efficiency.

When a byte or shorter data item is transferred to AL, the data is sign-extended or zero-extended and stored

as a 16-bit data item in AL. The data in AL can be handled either as word or byte long.

When a byte-processing arithmetic operation instruction is executed on AL, the high-order eight bits of AL

before operation are ignored. The high-order eight bits of the operation result all become zeroes.

The A register is not initialized by a reset. The A register holds an undefined value immediately after a

reset.

Figure 2.7-3 32-bit Data Transfer

Figure 2.7-4 AL-AH Transfer

XXXX

H

XXXX

H

8F74

H

2B52

H

DTB

A6

H

6

RW1

A61540

H

A6153E

H

MSB LSB

8F

H

2B

H

15

H

74

H

52

H

38

H

AH AL

MOVL A,@RW1+6

+

A before

execution

A after

execution

+6

RW1

A61540

H

A6153E

H

XXXX

H

1234

H

1234

H

1234

H

DTB

A6

H

8F

H

2B

H

15

H

74

H

52

H

38

H

MSB

LSB

MOVW A,@RW1+6

A before

execution

A after

execution