1 timer control status registers (high) (tmcsr:h), Timer control status registers (high) (tmcsr:h) – FUJITSU F2MCTM-16LX User Manual

Page 261

245

CHAPTER 14 16-BIT RELOAD TIMER

14.3.1

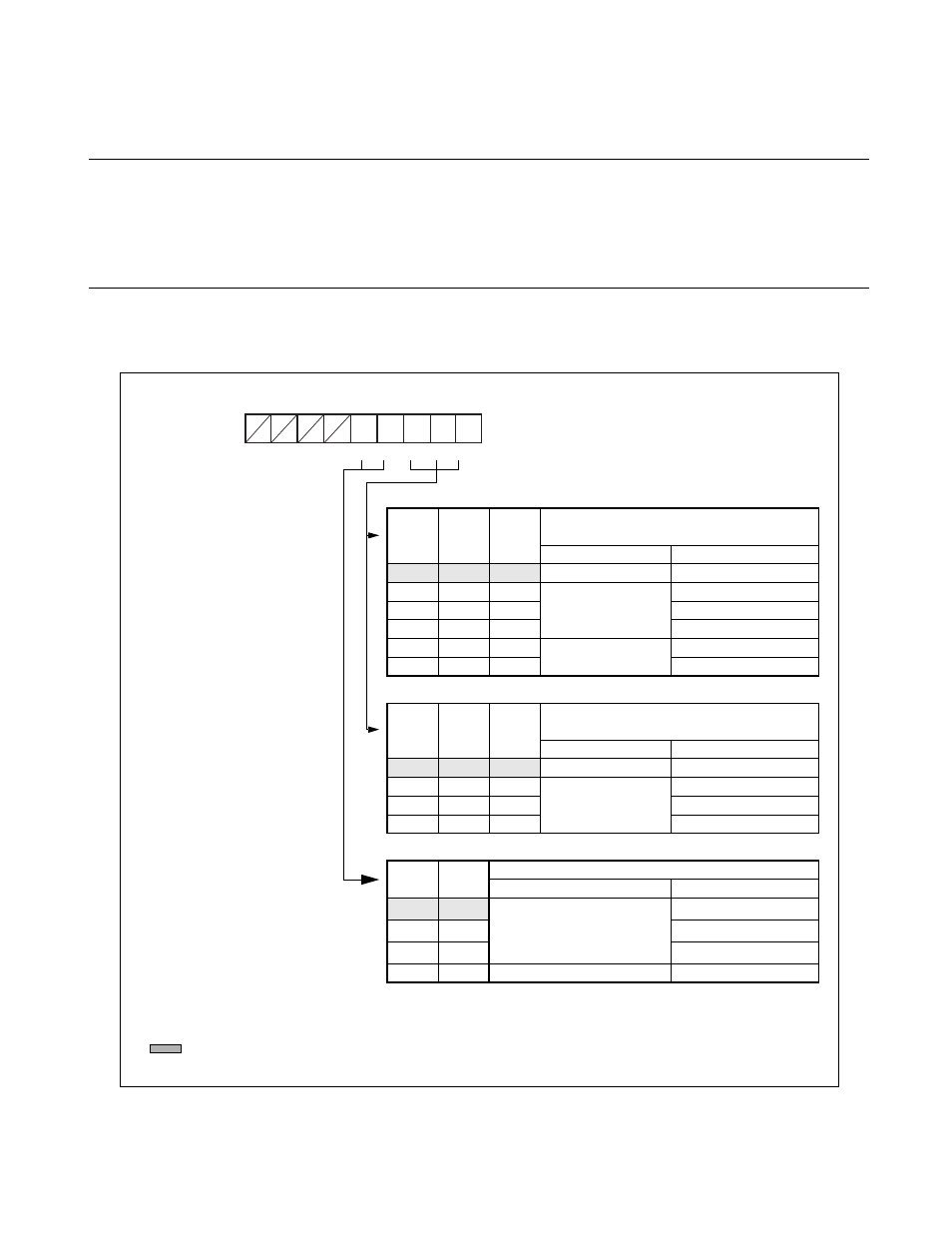

Timer Control Status Registers (High) (TMCSR:H)

The timer control status registers (High) (TMCSR:H) set the operation mode and count

clock.

This section also explains the bit 7 in the timer control status registers (Low)

(TMCSR:L).

■

Timer Control Status Registers (High) (TMCSR:H)

Figure 14.3-3 Timer Control Status Registers (High) (TMCSR:H)

12

13

11

10

9

8

14

XXXX0000

B

R/W R/W

R/W

−

−

−

− R/W R/W

7

15

TMCSR2 : 000065

H

TMCSR3 : 000067

H

MOD0

MOD1

MOD2

CSL0

CSL1

bit9

bit8

bit7

MOD2

MOD1

MOD0

Operating mode select bit (internal clock mode)

(CSL1, 0="00

B

", "01

B

", "10

B

")

Input pin function

Valid edge, level

0

0

0

Trigger disable

−

0

0

1

Trigger input

Rising edge

0

1

0

Falling edge

0

1

1

Both edges

1

X

0

Gate input

"L" level

1

X

1

"H" level

bit9

bit8

bit7

MOD2

MOD1

MOD0

Operating mode select bit (event count mode)

(CSL1, 0="11

B

")

Input pin function

Valid edge

X

0

0

−

−

X

0

1

Trigger input

Rising edge

X

1

0

Falling edge

X

1

1

Both edges

bit11

bit10

CSL1

CSL0

Count clock select bit

Count clock

Count clock cycle

0

0

Internal clock mode

2

1

T

0

1

2

3

T

1

0

2

5

T

1

1

Event count mode

External event clock

T: Machine cycle

R/W

: Read/Write

X

; Indeterminate

−

: Undefined

: Reset value

Address:

Reset value