Interrupt level mask register (ilm) – FUJITSU F2MCTM-16LX User Manual

Page 60

44

CHAPTER 2 CPU

■

Interrupt level mask register (ILM)

The ILM register consists of three bits, indicating the CPU interrupt masking level. An interrupt request is

accepted only when the level of the interrupt is higher than that indicated by these three bits. Level 0 is the

highest priority interrupt, and level 7 is the lowest priority interrupt (see Table 2.7-1 ). Therefore, for an

interrupt to be accepted, its level value must be smaller than the current ILM value. When an interrupt is

accepted, the level value of that interrupt is set in ILM. Thus, an interrupt of the same or lower level cannot

be accepted subsequently. ILM is initialized to all zeroes by a reset. An instruction may transfer an eight-bit

immediate value to the ILM register, but only the low-order three bits of that data are used.

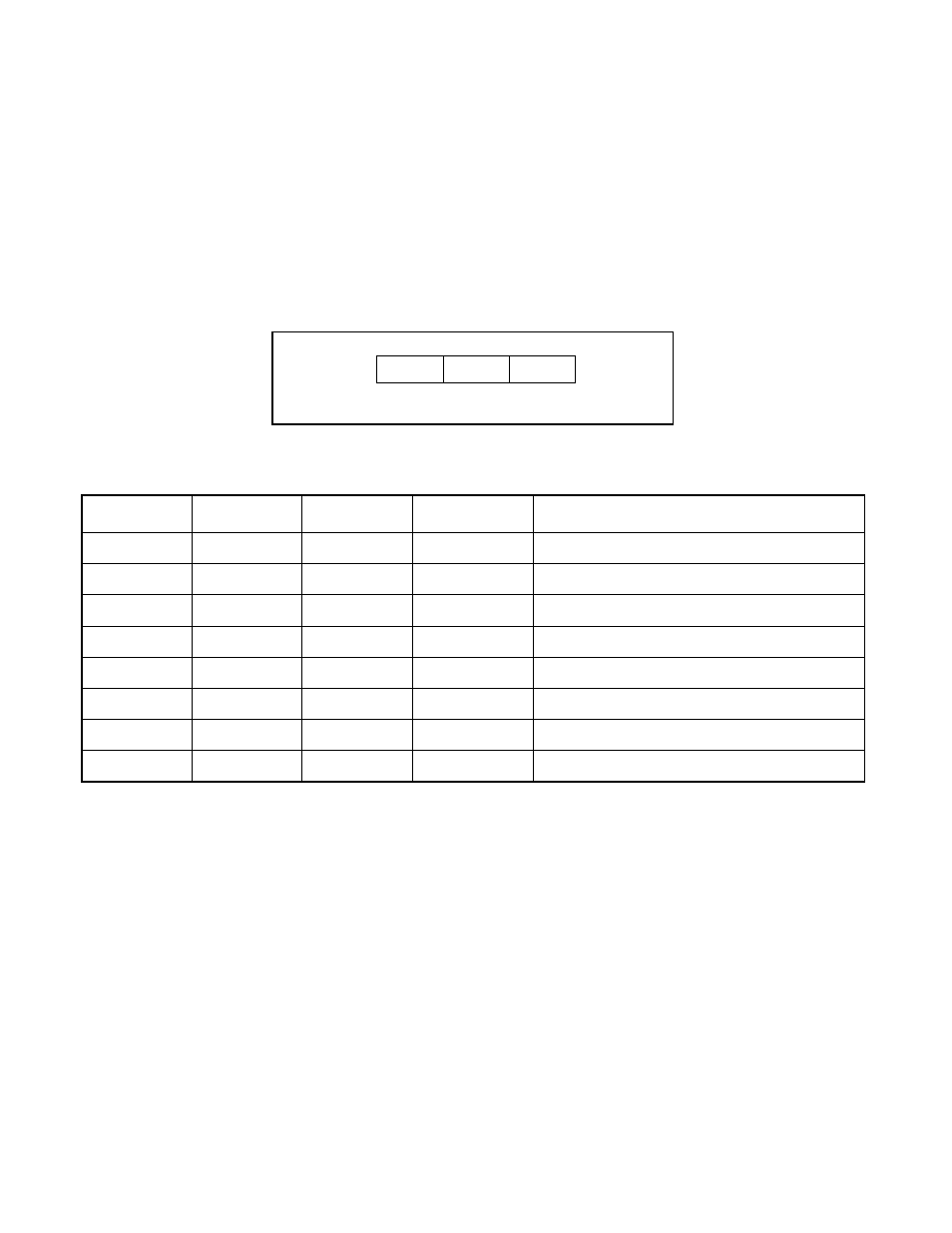

Figure 2.7-9 Interrupt Level Mask Register (ILM)

ILM2

ILM1

ILM0

: ILM

Initial value

0

0

0

Table 2.7-1 Levels Indicated by the Interrupt Level Mask (ILM) Register

ILM2

ILM1

ILM0

Level value

Acceptable interrupt level

0

0

0

0

Interrupt disabled

0

0

1

1

0 only

0

1

0

2

Level value smaller than 1

0

1

1

3

Level value smaller than 2

1

0

0

4

Level value smaller than 3

1

0

1

5

Level value smaller than 4

1

1

0

6

Level value smaller than 5

1

1

1

7

Level value smaller than 6