Operating state of 16-bit timer register – FUJITSU F2MCTM-16LX User Manual

Page 269

253

CHAPTER 14 16-BIT RELOAD TIMER

■

Operating State of 16-bit Timer Register

The operating state of the 16-bit timer register is determined by the timer operation enable bit in the timer

control status register (TMCSR:CNTE) and the WAIT signal. The operating states include the stop state,

start trigger input wait state (WAIT state), and RUN state.

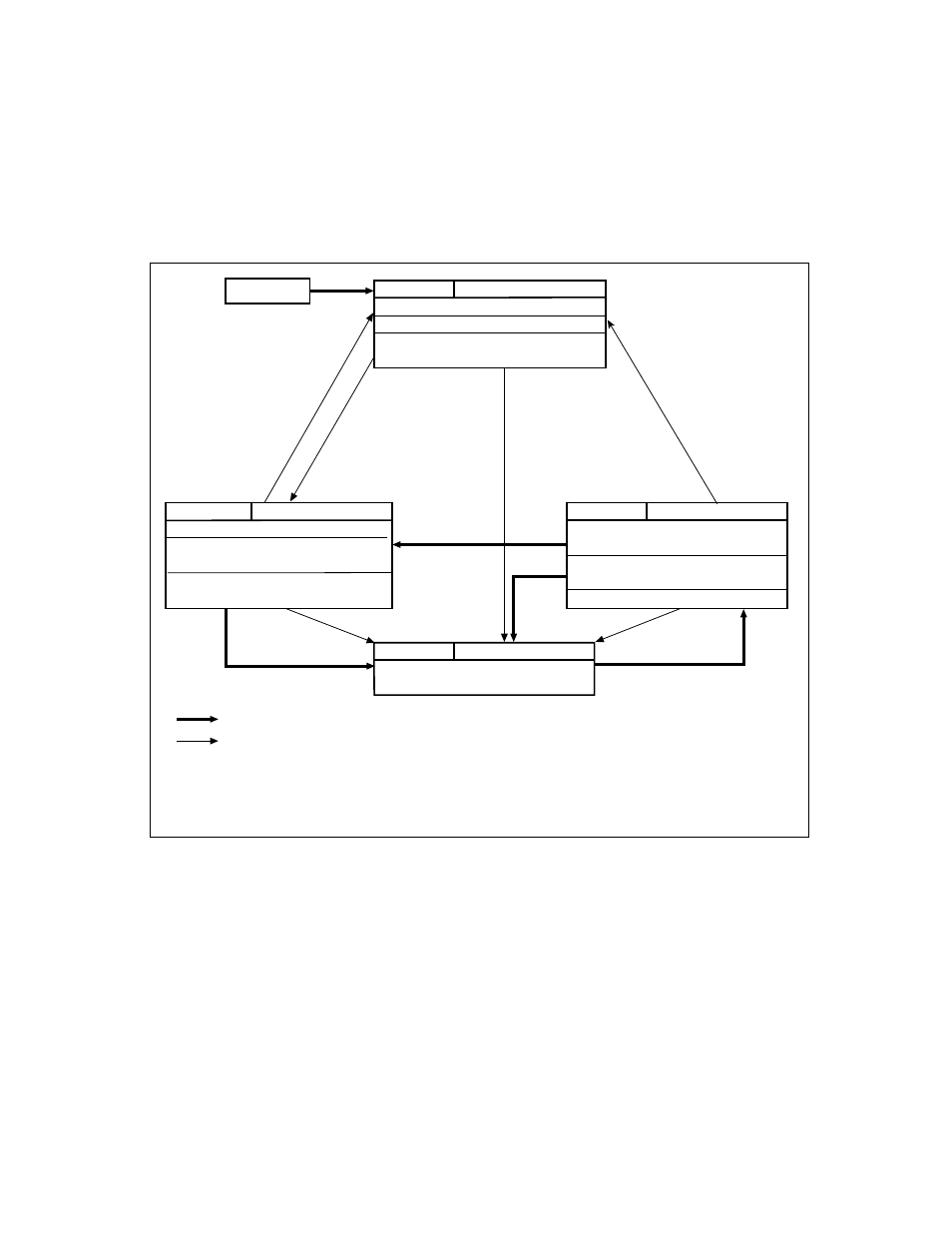

Figure 14.5-3 shows the state transition diagram for the 16-bit timer registers.

Figure 14.5-3 State Transition Diagram

CNTE=0

CNTE=0

CNTE=1

TRG=0

TRG=1

TRG=1

UF=1&

RELD=1

CNTE=1

TRG=1

UF=1&

RELD=0

CNTE=0, WAIT=1

LOAD

CNTE=1, WAIT=0

CNTE=1, WAIT=1

CNTE=1, WAIT=0

WAIT

TRG

CNTE

UF

RELD

STOP state

TIN pin: Input disable

TOUT pin: General-purpose I/O port

16-bit timer register:retain the value at stop

the value immediately after

resetting is undefined

Reset

WAIT state

RUN state

TIN pin: only trigger input is valid

16-bit timer register:retains the value at stop

the value immediately

after resetting is undefined

TOUT pin: outputs value of 16-bit

reload register

TIN pin:function as input pin of 16-bit

reload timer

TOUT pin:function as output pin of

16-bit reload timer

16-bit timer register: operation

Loads 16-bit reload register value to

16-bit timer register

(one-shot mode)

(reload mode)

(software trigger)

(software trigger)

Load ended

External trigger from TIN

: State transition by hardware

: State transition by register access

: WAIT signal (internal signal)

: Software trigger bit (TMCSR)

: Timer operation enable bit (TMCSR)

: Underflow generating flag bit (TMCSR)

: Reload select bit (TMCSR)