1 resets, Resets – FUJITSU F2MCTM-16LX User Manual

Page 136

120

CHAPTER 7 RESETS

7.1

Resets

If a reset is generated, the CPU immediately stops the current execution process and

waits for the reset to be cleared. The CPU then begins processing at the address

indicated by the reset vector.

The four causes of a reset are as follows

• Power-on reset

• External reset request via the RST pin

• Software reset request

• Watchdog timer overflow

• Low voltage detection reset request (product with "T"-suffix)

• CPU operation detection reset request (product with "T"-suffix)

• Clock supervisor reset request (MB90367/T(S))

■

Causes of a Reset

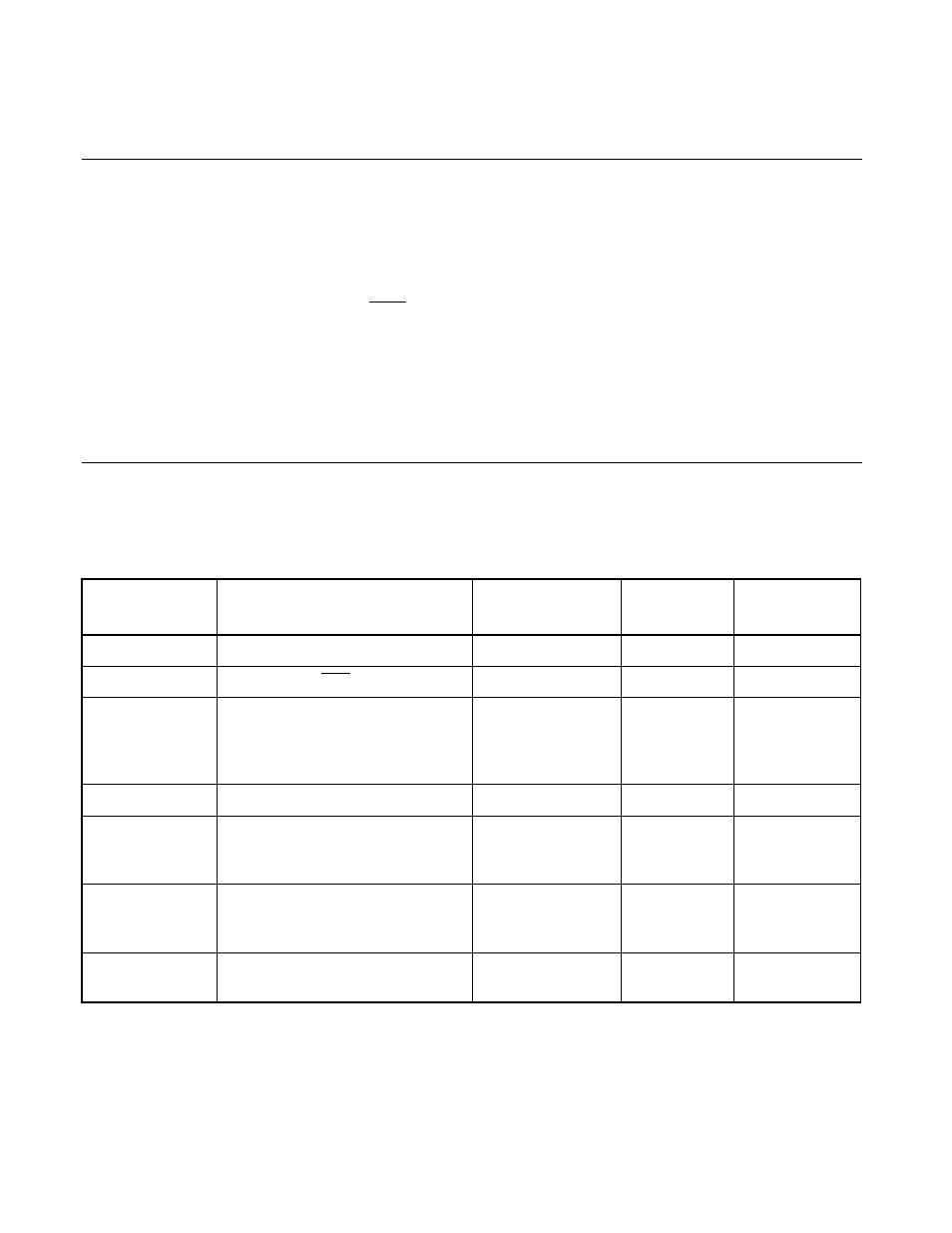

Table 7.1-1 lists the causes of a reset.

●

Power-on reset

A power-on reset is generated when the power is turned on. The oscillation stabilization wait times is fixed

to 2

16

oscillation clock cycles (2

16

/HCLK) (approx. 16.38 ms, oscillating at 4 MHz). When the oscillation

Table 7.1-1 Cause of a Reset

Reset Cause

Machine

clock

Watchdog

timer

Oscillation

stabilization wait

Power-on

At power on

Main clock (MCLK)

Stop

Yes

External pin

L level input to RST pin

Main clock (MCLK)

Stop

None

Software

Write "0" to internal reset signal

generation bit (RST) of low-power

consumption mode control register

(LPMCR)

Main clock (MCLK)

Stop

None

Watchdog timer

Watchdog timer overflow

Main clock (MCLK)

Stop

None

Low voltage

detection reset

(with "T"-suffix)

When low voltage (4.0 V

± 0.3 V) is

detected

Main clock (MCLK)

Stop

None

CPU operation

detection reset

(with "T"-suffix)

When CPU operation detection

counter overflows

Main clock (MCLK)

Stop

None

Clock supervisor

reset

When failure of main clock/subclock is

detected

Internal CR

oscillation clock

Stop

None

MCLK: Main clock (oscillation clock frequency divided by 2)