FUJITSU F2MCTM-16LX User Manual

Page 606

590

APPENDIX

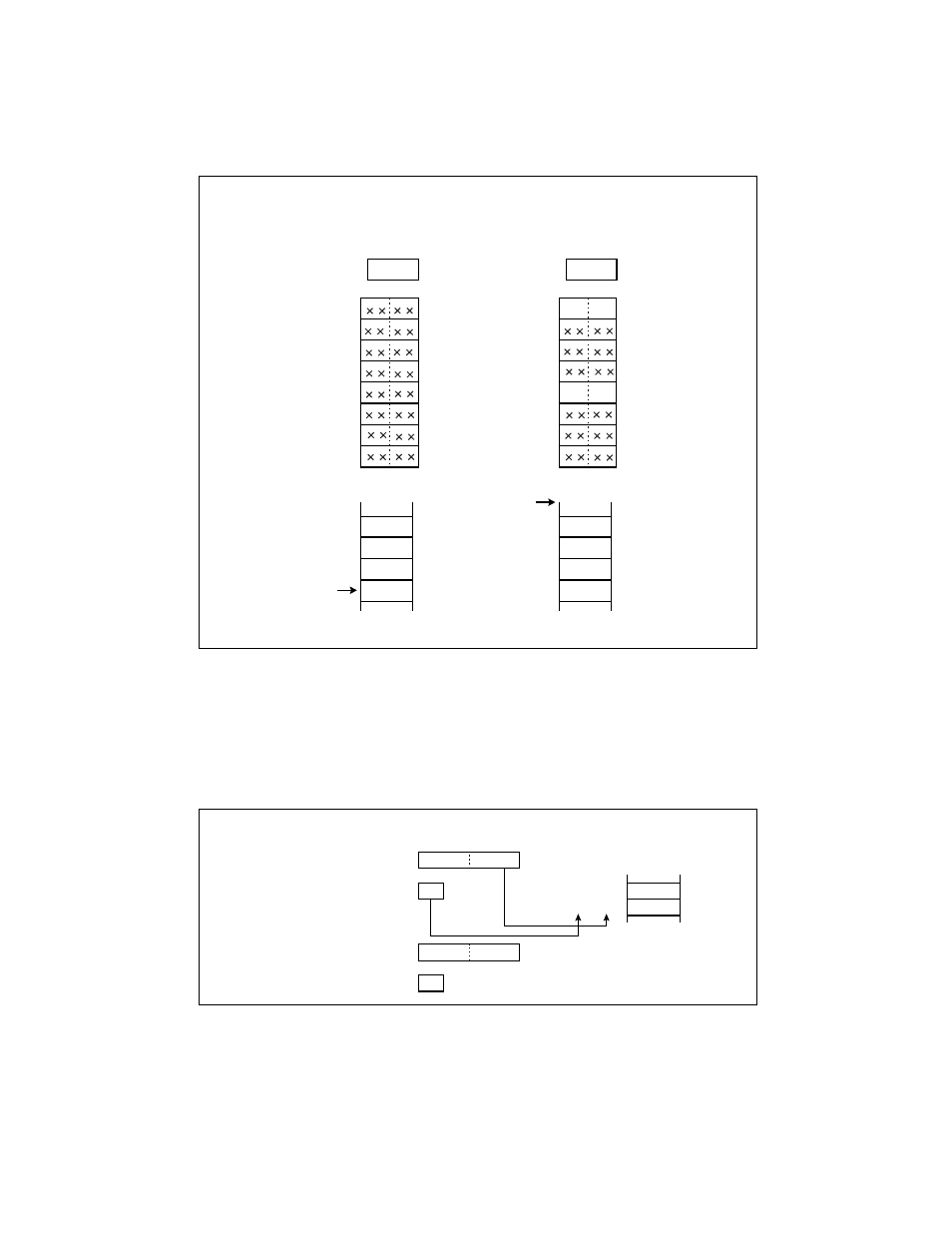

Figure B.4-9 Example of Register List (rlst)

●

Accumulator indirect addressing (@A)

Memory is accessed using the address indicated by the contents of the low-order bytes (16 bits) of the

accumulator (AL). Address bits 16 to 23 are specified by a mnemonic in the data bank register (DTB).

Figure B.4-10 Example of Accumulator Indirect Addressing (@A)

POPW RW0, RW4

3 4 F A

SP

RW0

RW1

RW2

RW3

RW4

RW5

RW6

RW7

0 4

0 3

34FDH

34FCH

34FEH

0 2

0 1

34FBH

34FAH

SP

3 4 F E

SP

0 1

0 2

RW0

RW1

RW2

RW3

RW4

RW5

RW6

RW7

0 3

0 4

0 4

0 3

34FDH

34FCH

34FEH

0 2

0 1

34FBH

34FAH

SP

Before execution

After execution

Memory space

Memory space

(This instruction transfers memory data indicated by the SP to multiple

word registers indicated by the register list.)

MOVW A, @A

0 7 1 6

A

2 5 3 4

DTB

F F

E E

0 7 1 6

A

F F E E

DTB

B B

B B

BB2535H

BB2534H

Before execution

After execution

Memory space

(This instruction reads data by accumulator indirect addressing and stores it in A.)

- XG Series P3NK-4452-01ENZD (614 pages)

- FPCAC14C (1 page)

- MCJ3230SS (161 pages)

- MBA3073NC (138 pages)

- T5140 (102 pages)

- T5140 (76 pages)

- MAM3367MC/MP (152 pages)

- MPC3045AH (185 pages)

- MB2142-02 (23 pages)

- MB15F86UL (6 pages)

- MHS2030AT (40 pages)

- MHW2100BS (296 pages)

- MHK2060AT (227 pages)

- Disk Drives MHK2060AT (227 pages)

- MCM3064SS (170 pages)

- Mainboard D1561 (45 pages)

- MHC2040AT (219 pages)

- D1961 (45 pages)

- DISK DRIVES MHM2100AT (231 pages)

- MHR2010AT (250 pages)

- MHZ2120BJ (320 pages)

- MCE3064AP (175 pages)

- LQFP-64P (16 pages)

- Solaris PCI GigabitEthernet 3.0 (115 pages)

- MAY2036RC (94 pages)

- MAB3091 (142 pages)

- MPE3XXXAT (191 pages)

- MHV2040AH (40 pages)

- MHW2040AC (278 pages)

- ETERNUSmgr P2X0-0202-01EN (64 pages)

- VSS Hardware Provider 2.1 (134 pages)

- MAG3182FC (61 pages)

- MAU3147NC/NP (130 pages)

- MAX3147RC (94 pages)

- MHV2160BT (296 pages)

- MHV2040AT (280 pages)

- MAW3300NC/NP (130 pages)

- DeskPower E623 (50 pages)

- MAG3182LC (133 pages)

- OPTICAL DISK DRIVES MDG3064UB (42 pages)

- MHF2021AT (225 pages)

- MHR2040AT (40 pages)

- Single Drive FTM7926FB (1 page)

- PG-FCS103 (98 pages)

- MAS3735FC (114 pages)