1 watch timer control register (wtc), Watch timer control register (wtc) – FUJITSU F2MCTM-16LX User Manual

Page 289

273

CHAPTER 15 WATCH TIMER

15.3.1

Watch Timer Control Register (WTC)

This section explains the functions of the watch timer control register (WTC).

■

Watch Timer Control Register (WTC)

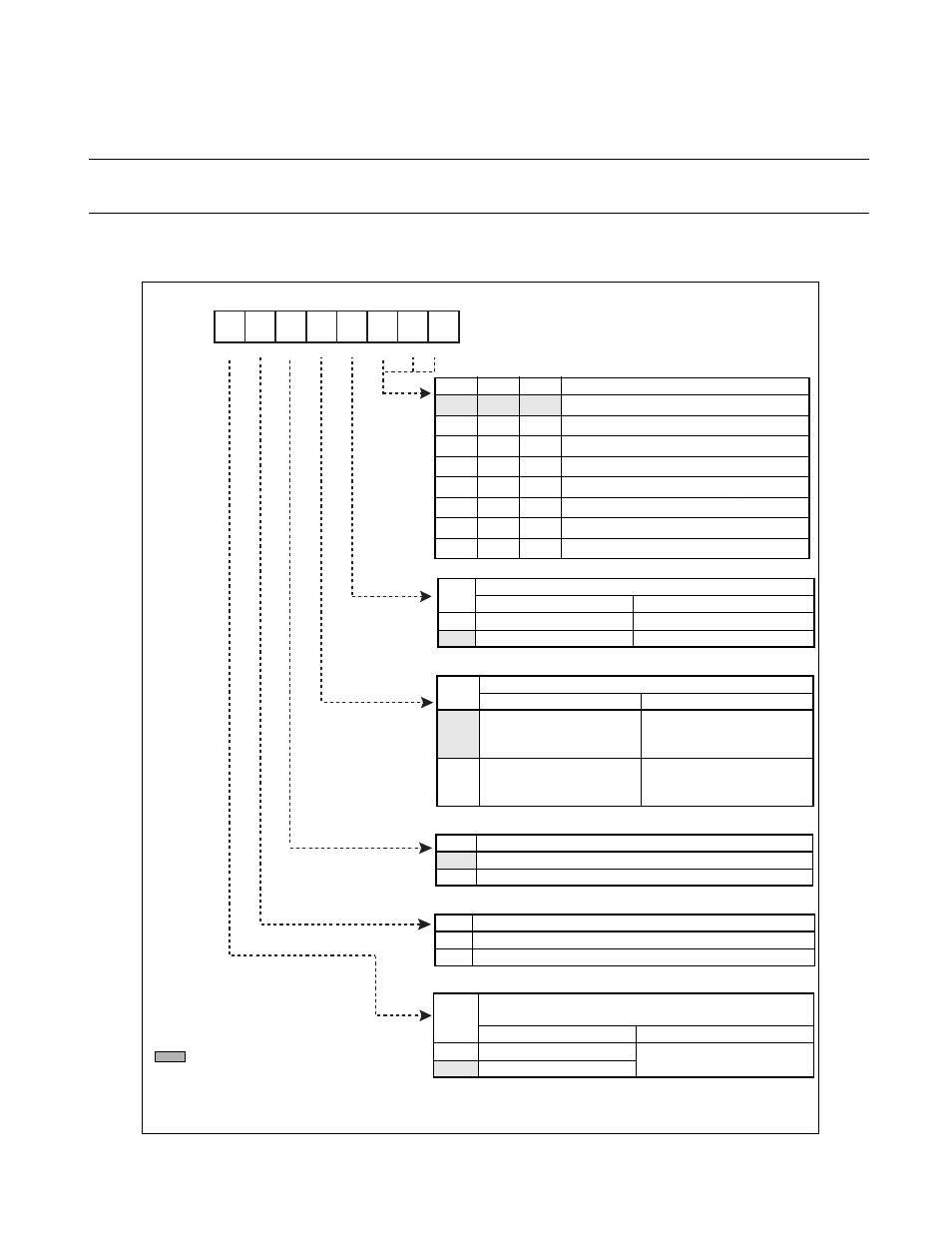

Figure 15.3-2 Watch Timer Control Register (WTC)

1X001000

B

4

5

3

2

1

0

6

7

R/W

R/W

R/W

R/W

R/W

R/W

R

R/W

0000AA

H

WTC0

WTC1

WTC2

WTR

WTOF

WTIE

SCE

WDCS

bit2

bit1

bit0

WTC2 WTC1 WTC0

Interval time select bit

0

0

0

2

8

/SCLK(31.25 ms)

0

0

1

2

9

/SCLK(62.5 ms)

0

1

0

2

10

/SCLK(125 ms)

0

1

1

2

11

/SCLK(250 ms)

1

0

0

2

12

/SCLK(500 ms)

1

0

1

2

13

/SCLK(1.0 s)

1

1

0

2

14

/SCLK(2.0 s)

1

1

1

2

15

/SCLK(4.0 s)

bit3

WTR

Watch timer clear bit

Read

Write

0

⎯

Clear watch timer counter

1

"1" is always read.

No effect

Reset value

R/W

: Read/Write

R

: Read only

X

: Undefined

SCLK : Subclock

: Reset value

bit4

WTOF

Overflow flag bit

Read

Write

0

No overflow of the bit

corresponding to set interval

time

Clears WTOF bit

1

Overflow of the bit

corresponding to set interval

time

No effect

bit5

WTIE

Overflow interrupt enable bit

0

Interrupt request disable

1

Interrupt request enable

bit6

SCE

Oscillation stabilization wait time end bit

0

Oscillation stabilization wait state

1

Oscillation stabilization wait time end

bit7

WDCS

Watchdog clock select bit

(input clock of watchdog timer)

Main or PLL clock mode

Subclock mode

0

Watch timer

Set "0"

1

Timebase timer

The parenthesized values are provided when subclock operates at 8.192 kHz.

Address