FUJITSU F2MCTM-16LX User Manual

Page 471

455

■

Control status register (CSR-upper)

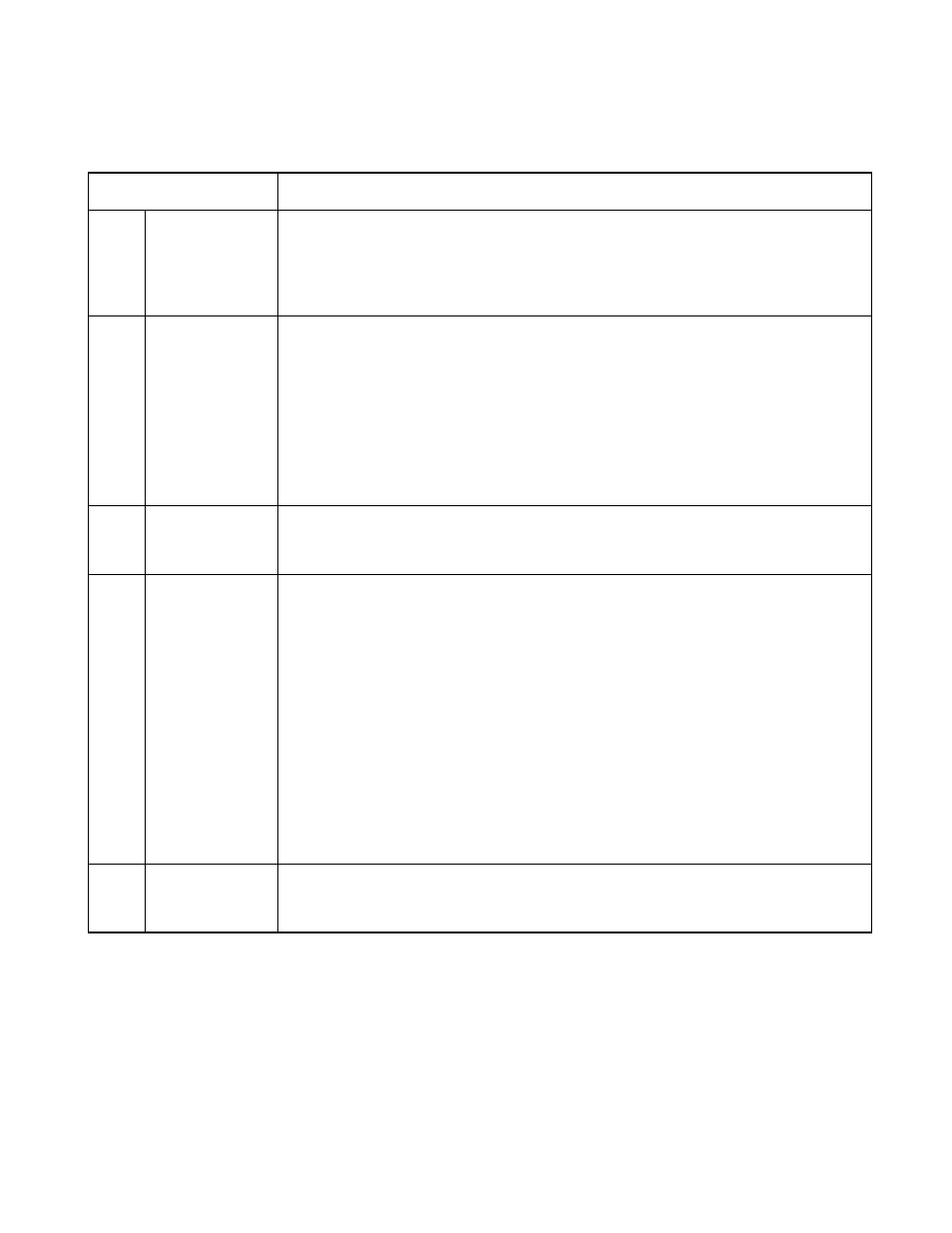

Table 21.4-2 Function of Each Bit of the Control Status Register (CSR:H)

Bit Name

Function

bit15

TS:

Transmit status

bit

This bit indicates whether a message is being transmitted.

At read:

0: Message not being transmitted

1: Message being transmitted

This bit is set 0 even while error and overload frames are transmitted.

bit14

RS:

Receive status bit

This bit indicates whether a message is being received.

At read:

0: Message not being received

1: Message being received

•

While a message is on the bus, this bit becomes 1. Therefore, this bit is also 1 while a

message is being transmitted. This bit does not necessarily indicates whether a receiving

message passes through the acceptance filter.

•

As a result, when this bit is 0, it implies that the bus operation is stopped (HALT = 1);

the bus is in the intermission/bus idle or a error/overload frame is on the bus.

bit13

to

bit11

Undefined bits

When reading: The value is undefined.

When writing: No effect

bit10

NT:

Node status

transition flag

When the node status changes from increment transition or off bus into error active, this bit is

set to "1". The condition that this bit is set to "1" is as follows. At this time, the interruption

is generated for the node status interruption permission bit (NIE) = "1".

1) Error active ("00

B

")

→ Warning ("01

B

")

2) Warning ("01

B

")

→ Error passive ("10

B

")

3) Error passive ("10

B

")

→ Bus off ("11

B

")

4) Bus off ("11

B

")

→ Error active ("00

B

")

Note:

In parentheses, the value of NS1 and the NS0 bit is indicated.

At Write:

"0": Cleared

"1": Not possible to set (No effect)

At read by the instruction of the read-modify-write type:

Always read "1".

bit9

bit8

NS1, NS0:

Node status bits

These bits indicate the current node status.

For detail information, see "21.4.3 Correspondence between Node Status Bit and Node

Status".