1 overview of dtp/external interrupt, Overview of dtp/external interrupt – FUJITSU F2MCTM-16LX User Manual

Page 330

314

CHAPTER 17 DTP/EXTERNAL INTERRUPTS

17.1

Overview of DTP/External Interrupt

The DTP/external interrupt sends interrupt requests from external peripheral devices or

data transfer requests to the CPU to generate an external interrupt request, or starts the

EI

2

OS.

■

DTP/External Interrupt Function

The DTP/external interrupt follows the same procedure as resource interrupts to send interrupt requests

from external peripheral devices to the CPU to generate an external interrupt request, or starts the EI

2

OS.

If the EI

2

OS is disabled in the interrupt control register (ICR: ISE=0), the external interrupt function is

enabled, branching to interrupt processing.

If the EI

2

OS is enabled, the DTP function is enabled and automatic data transfer is performed, branching to

interrupt processing after the completion of data transfer for the specified number of times.

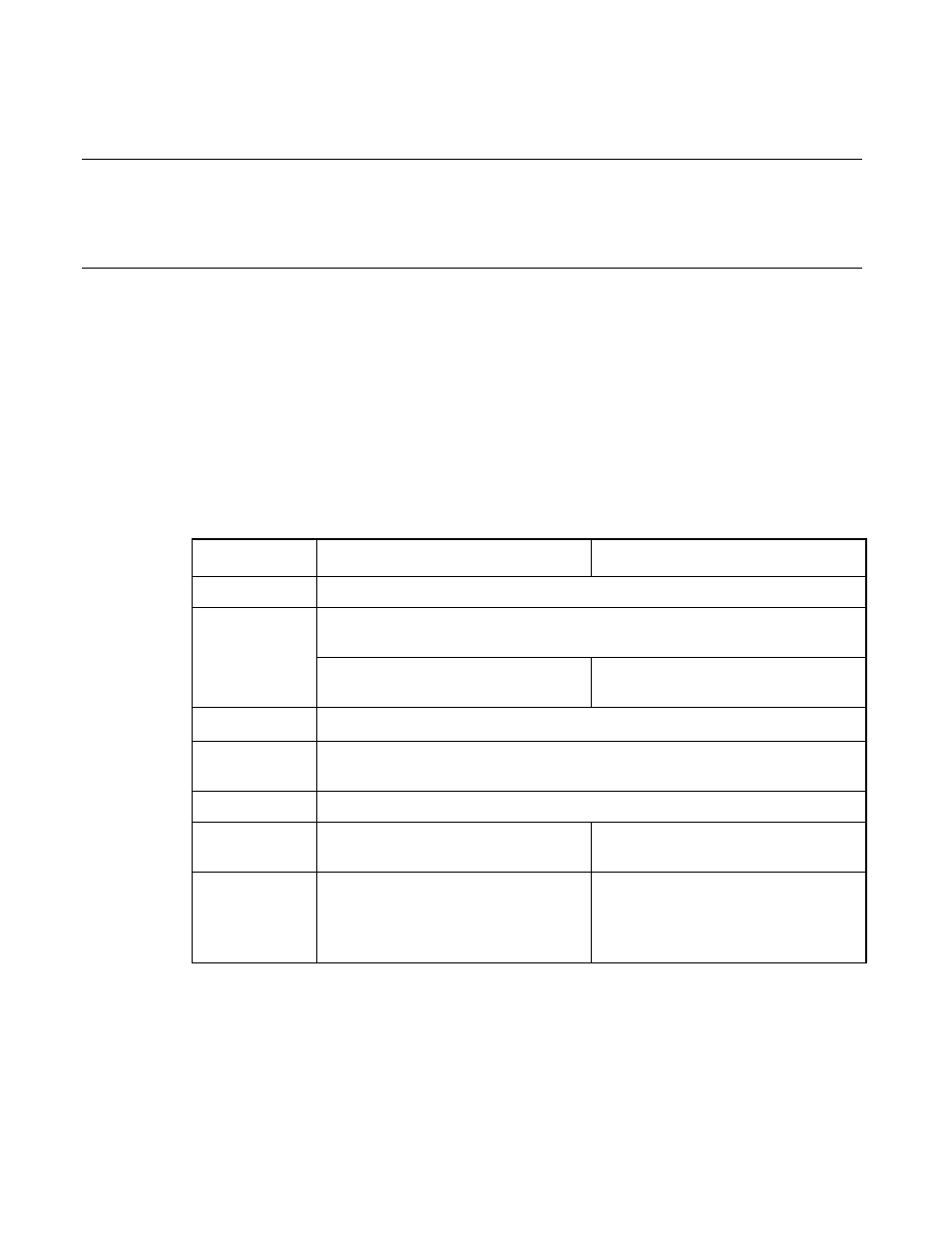

Table 17.1-1 shows an overview of the DTP/external interrupt.

Table 17.1-1 Overview of DTP/External Interrupt

External Interrupt

DTP Function

Input pin

8 pins : INT8, INT9R, INT10, INT11, INT12R, INT13, INT14R, INT15R

Interrupt factor

The interrupt factor is set in unit of pins using the detection level setting registers

(ELVR1).

Input of High level, Low level, rising

edge, or falling edge

Input of High level or Low level

Interrupt number

#26(1A

H

), #28(1C

H

)

Interrupt control

The interrupt request output is enabled/disabled using the DTP/external interrupt

enable register (ENIR1).

Interrupt flag

The interrupt factor is held using the DTP/external interrupt factor register (EIRR1).

Processing

selection

The EI

2

OS is disabled. (ICR: ISE=0)

The EI

2

OS is enabled. (ICR: ISE=1)

Processing

contents

A branch is caused to the external

interrupt processing routine.

EI

2

OS performs automatic data transfer

and completes the specified number of

time for data transfers, causing a branch

to the interrupt processing.