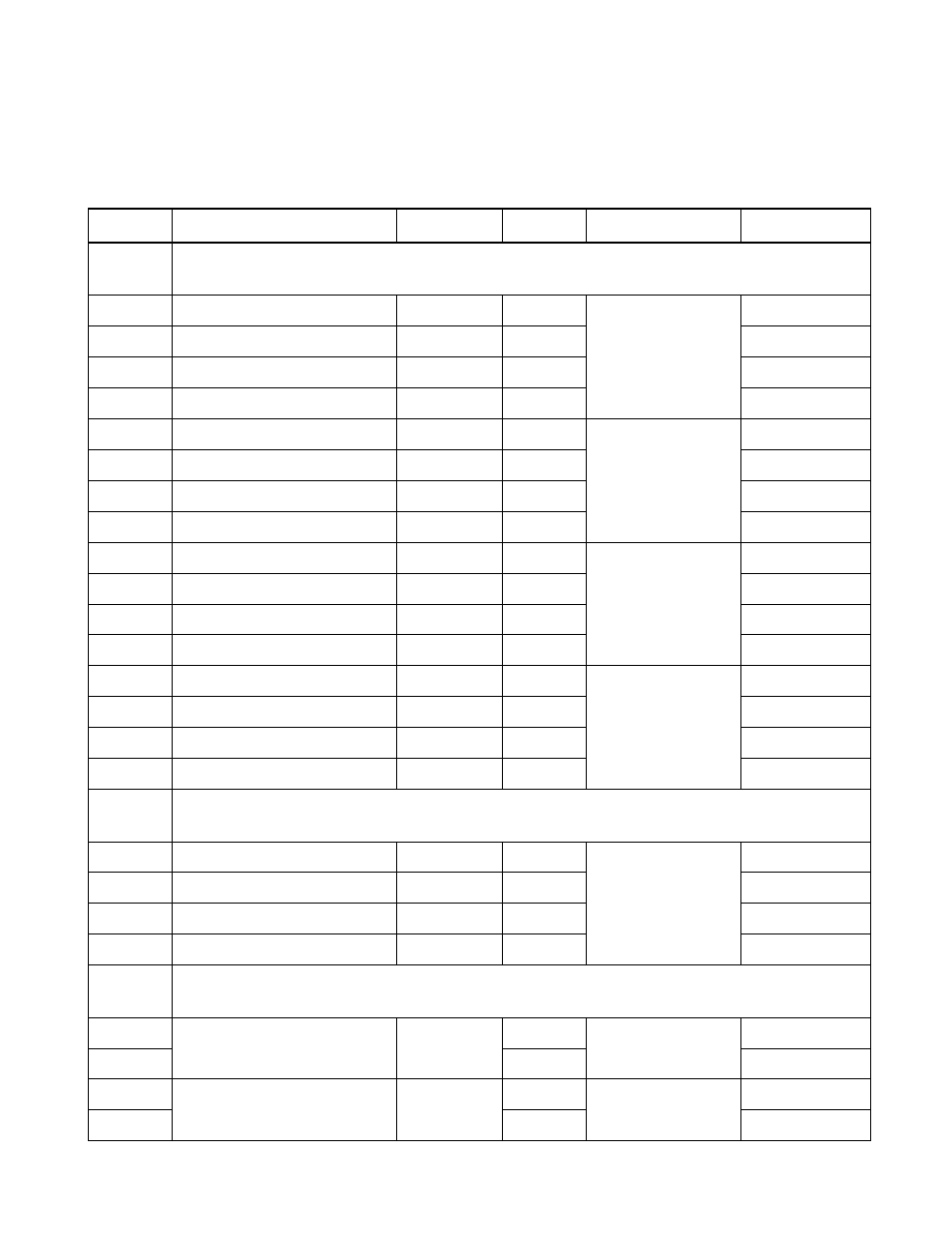

I/o map (79xx - 7fxx addresses) – FUJITSU F2MCTM-16LX User Manual

Page 589

573

APPENDIX A I/O Maps

■

I/O map (79XX - 7FXX addresses)

Table A-2 I/O Map (7900

H

- 7FFF

H

) (1/3)

Address

Register

Abbreviation

Access

Peripheral

Initial value

7900

H

to

7917

H

Reserved

7918

H

Reload register LC

PRLLC

R/W

16-bit

PPG C/D

XXXXXXXX

B

7919

H

Reload register HC

PRLHC

R/W

XXXXXXXX

B

791A

H

Reload register LD

PRLLD

R/W

XXXXXXXX

B

791B

H

Reload register HD

PRLHD

R/W

XXXXXXXX

B

791C

H

Reload register LE

PRLLE

R/W

16-bit

PPG E/F

XXXXXXXX

B

791D

H

Reload register HE

PRLHE

R/W

XXXXXXXX

B

791E

H

Reload register LF

PRLLF

R/W

XXXXXXXX

B

791F

H

Reload register HF

PRLHF

R/W

XXXXXXXX

B

7920

H

Input capture 0

IPCP0

R

Input Capture 0/1

XXXXXXXX

B

7921

H

Input capture 0

IPCP0

R

XXXXXXXX

B

7922

H

Input capture 1

IPCP1

R

XXXXXXXX

B

7923

H

Input capture 1

IPCP1

R

XXXXXXXX

B

7924

H

Input capture 2

IPCP2

R

Input Capture 2/3

XXXXXXXX

B

7925

H

Input capture 2

IPCP2

R

XXXXXXXX

B

7926

H

Input capture 3

IPCP3

R

XXXXXXXX

B

7927

H

Input capture 3

IPCP3

R

XXXXXXXX

B

7928

H

to

793F

H

Reserved

7940

H

Timer data 0

TCDT0

R/W

I/O Timer 0

0 0 0 0 0 0 0 0

B

7941

H

Timer data 0

TCDT0

R/W

0 0 0 0 0 0 0 0

B

7942

H

Timer control 0

TCCSL0

R/W

0 0 0 0 0 0 0 0

B

7943

H

Timer control 0

TCCSH0

R/W

0XXXXXXX

B

7944

H

to

794B

H

Reserved

794C

H

Timer 2/reload 2

TMR2/

TMRLR2

R, W

16-bit Reload

Timer 2

XXXXXXXX

B

794D

H

R, W

XXXXXXXX

B

794E

H

Timer 3/reload 3

TMR3/

TMRLR3

R, W

16-bit Reload

Timer 3

XXXXXXXX

B

794F

H

R, W

XXXXXXXX

B