FUJITSU F2MCTM-16LX User Manual

Page 26

10

CHAPTER 1 OVERVIEW

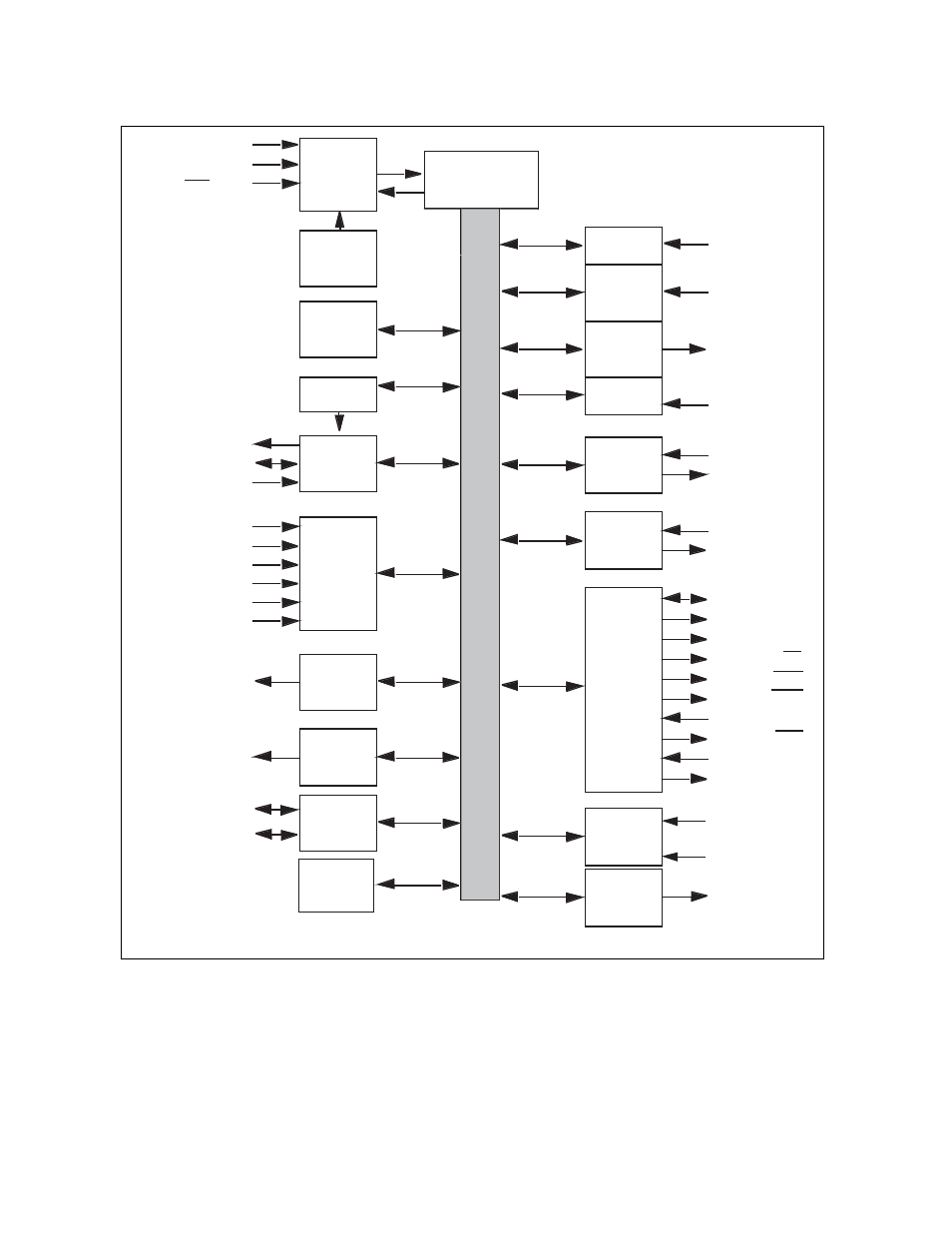

Figure 1.2-2 Block Diagram of Evaluation Chip (MB90V340A-103/104)

(INT15R to INT8R)

INT15 to INT8

INT7 to INT0

CKOT

SCL1 , SCL0

SDA1 , SDA0

PPGF to PPG0

DA01 , DA00

X0,X1

X0A,X1A*

RST

FRCK0

IN7 to IN0

OUT7 to OUT0

FRCK1

RX2 to RX0

TX2 to TX0

TIN3 to TIN0

TOT3 to TOT0

SOT4 to SOT0

SCK4 to SCK0

SIN4 to SIN0

AVcc

AVss

AN23 to AN0

AVRH

AVRL

ADTG

AD15 to AD00

A23 to A16

ALE

RD

WRL

WRH

HRQ

HAK

RDY

CLK

Clock

control

Prescaler

(5 channels)

8-/10-bit

A/D

converter

24 channels

10-bit D/A

converter

2 channels

8-/16-bit

PPG

16 channels

Int

e

rn

al d

a

ta

b

u

s

16-bit

I/O timer 0

Input

capture

8 channels

Output

compare

8 channels

16-bit

I/O timer 1

CAN

controller

3 channels

16-bit

reload timer

4 channels

External

bus

DTP/

external

interrupt

Clock

monitor

F

2

MC-16LX core

I

2

C

Interface

2 channels

*

: Support MB90V340A-104 only

CR

oscillation

circuit

RAM 30KB

UART

5 channels

DMA

- XG Series P3NK-4452-01ENZD (614 pages)

- FPCAC14C (1 page)

- MCJ3230SS (161 pages)

- MBA3073NC (138 pages)

- T5140 (102 pages)

- T5140 (76 pages)

- MAM3367MC/MP (152 pages)

- MPC3045AH (185 pages)

- MB2142-02 (23 pages)

- MB15F86UL (6 pages)

- MHS2030AT (40 pages)

- MHW2100BS (296 pages)

- MHK2060AT (227 pages)

- Disk Drives MHK2060AT (227 pages)

- MCM3064SS (170 pages)

- Mainboard D1561 (45 pages)

- MHC2040AT (219 pages)

- D1961 (45 pages)

- DISK DRIVES MHM2100AT (231 pages)

- MHR2010AT (250 pages)

- MHZ2120BJ (320 pages)

- MCE3064AP (175 pages)

- LQFP-64P (16 pages)

- Solaris PCI GigabitEthernet 3.0 (115 pages)

- MAY2036RC (94 pages)

- MAB3091 (142 pages)

- MPE3XXXAT (191 pages)

- MHV2040AH (40 pages)

- MHW2040AC (278 pages)

- ETERNUSmgr P2X0-0202-01EN (64 pages)

- VSS Hardware Provider 2.1 (134 pages)

- MAG3182FC (61 pages)

- MAU3147NC/NP (130 pages)

- MAX3147RC (94 pages)

- MHV2160BT (296 pages)

- MHV2040AT (280 pages)

- MAW3300NC/NP (130 pages)

- DeskPower E623 (50 pages)

- MAG3182LC (133 pages)

- OPTICAL DISK DRIVES MDG3064UB (42 pages)

- MHF2021AT (225 pages)

- MHR2040AT (40 pages)

- Single Drive FTM7926FB (1 page)

- PG-FCS103 (98 pages)

- MAS3735FC (114 pages)