FUJITSU F2MCTM-16LX User Manual

Page 115

99

CHAPTER 5 CLOCKS

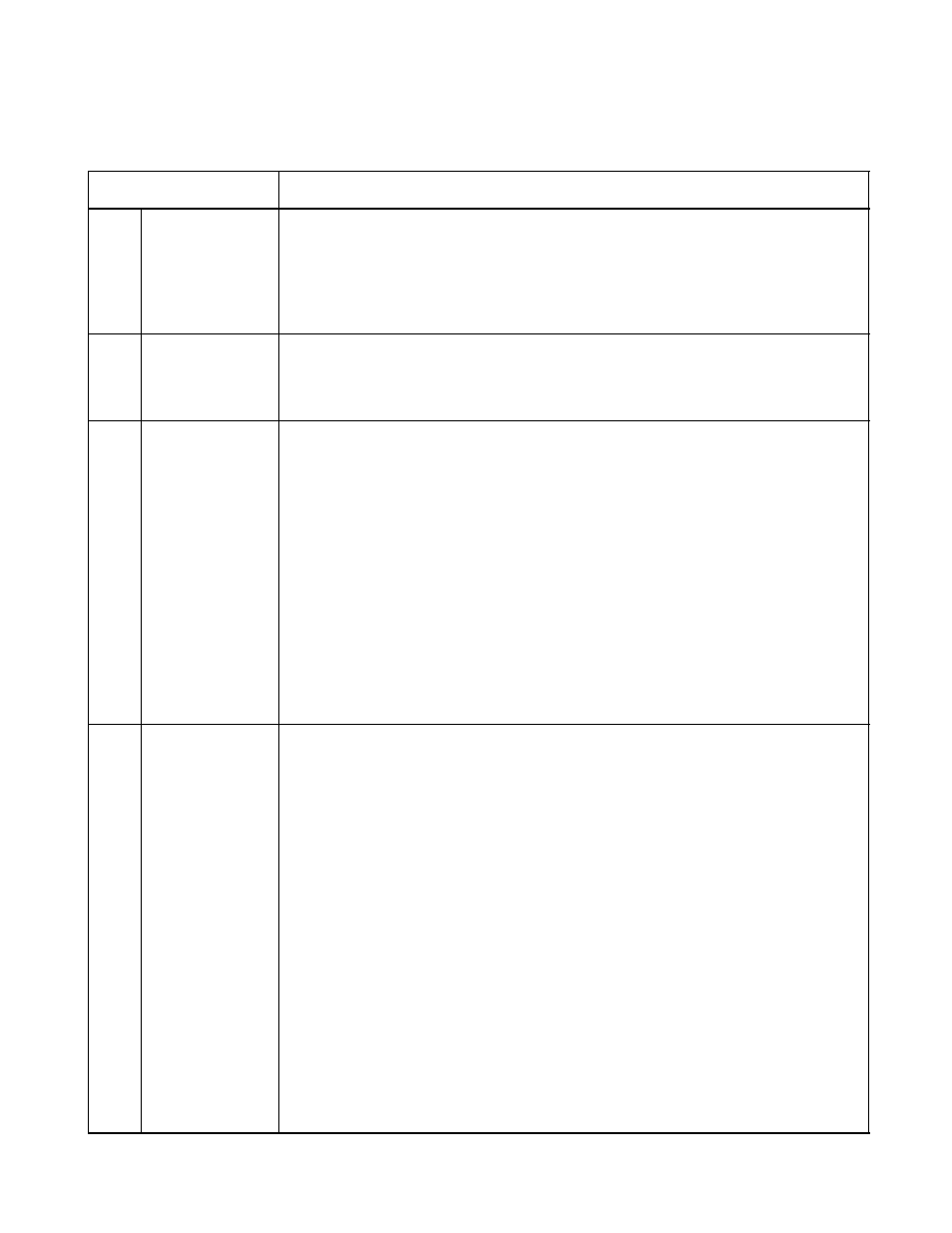

Table 5.3-1 Functions of Clock Selection Register (CKSCR) (1/2)

Bit name

Function

bit15

SCM:

Sub clock operation

flag bit

The bit indicates the main clock or subclock currently selected as the machine clock.

When the sub clock operation flag bit (CKSCR: SCM) is "0" and the sub clock select bit

(CKSCR: SCS) is "1", it indicates that the machine clock is currently switching from

subclock to main clock. When the sub clock operation flag bit (CKSCR: SCM) is "1" and the

sub clock select bit (CKSCR: SCS) is "0", it indicates that the machine clock is currently

switching from main clock to subclock. (The writing operation will not be affected.)

bit14

MCM:

PLL clock operation

flag bit

The bit indicates the main clock or PLL clock currently selected as the machine clock.

When the PLL clock operation flag bit (CKSCR: MCM) is "1" and the PLL clock select bit

(CKSCR: MCS) is "0", it indicates that the oscillation stabilization wait time of the PLL clock

is currently being taken. (The writing operation will not be affected.)

bit13

bit12

WS1, WS0:

Oscillation

stabilization wait

time select bits

These bits are used to select an oscillation stabilization wait time required for the oscillation

clock when the stop mode is canceled, when transition occurs from subclock mode to main

clock mode, or when transition occurs from subclock mode to PLL clock mode.

These bits are used to select one from four timebase timer outputs.

Any reset causes the bit to return to the reset value.

Note: Set the oscillation stabilization wait time to an appropriate value depending on the

oscillator used. See 7.2.1 Reset Factors and Oscillation Stabilization Wait Times.

The oscillation stabilization wait time taken when the clock mode is switched from

main clock to PLL clock is fixed at 2

14

/HCLK (about 4.1 ms during operation at an

oscillation clock frequency of 4 MHz).When the CPU switches from subclock mode to

PLL clock mode or when it returns from PLL stop mode to PLL clock mode, the

oscillation stabilization wait time follows the values specified in these bits.

The PLL clock requires an oscillation stabilization wait time of at least 2

14

/HCLK. For

switching from subclock mode to PLL clock mode and transiting to the PLL stop

mode, therefore, set these bits to "10

B

" or "11

B

".

bit11

SCS:

Sub clock select bit

This bit indicates the main clock or sub clock to be selected as the machine clock.

When the machine clock is switched from the main clock to the subclock (CKSCR: SCS = 1

→ 0), the main clock mode changes to the subclock mode of 1/SCLK (32.768 kHz oscillation

clock frequency, operating at 4 division: approx. 130

µs) in synchronization with the

subclock.

When the machine clock is switched from the subclock to the main clock (CKSCR: SCS = 0

→ 1), the clock mode changes from subclock mode to main clock mode after the main clock

oscillation stabilization wait time is generated.Timebase timer is cleared automatically.

Any reset causes the bit to return to the reset value.

Notes:

1) When both of the MCS and SCS bits contain 0, the SCS bit supersedes the MCS bit,

thereby setting the subclock mode.

2) If both the subclock select bit (CKSCR: SCS) and PLL clock select bit (CKSCR: MCS)

contain 0, the sub clock is preferred.

3) When switching from the main clock to subclock (CKSCR: SCS = 1

→ 0), use the

timebase timer interrupt enable bit (TBTC: TBIE) or interrupt level mask register (ILM:

ILM2 to 0) to disable timebase timer interrupts before writing 0 to the subclock select bit.

4) The 2

14

/SCLK sub clock oscillation stabilization wait time (32.768 kHz oscillation clock

frequency, operating at 4 division: approx. 2 s) is generated at power on or at cancellation

of the stop mode.If the clock mode is switched from main clock mode to subclock mode,

therefore, the oscillation stabilization wait time is generated.