1 sleep mode, Sleep mode – FUJITSU F2MCTM-16LX User Manual

Page 161

145

CHAPTER 8 LOW-POWER CONSUMPTION MODE

8.5.1

Sleep Mode

This mode causes the CPU operating clock to stop during operation in each clock

mode. The CPU stops, and peripheral function operates.

■

Switching to Sleep Mode

Writing 1 in the SLP bit and 0 in the STP bit of the low-power consumption mode control register

(LPMCR) triggers a switch to a sleep mode according to setting of the MCS and SCS bits in the clock

selection register (CKSCR). Table 8.5-2 shows the correspondence between MCS and SCS bits in the clock

selection register (CKSCR) and sleep mode.

Note:

When 1 is written to the SLP and STP bits of the low-power consumption mode control register

(LPMCR) at the same time, the STP bit setting overrides the SLP bit setting and the mode switches to

the stop mode. When 1 is written to the SLP bit and 0 is written to the TMD bit at the same time, the

TMD bit setting overrides the SLP bit setting and the mode switches to the timebase timer mode or

watch mode.

●

Data retention function

In a sleep mode, the contents of dedicated registers, such as accumulators, and the internal RAM are

retained.

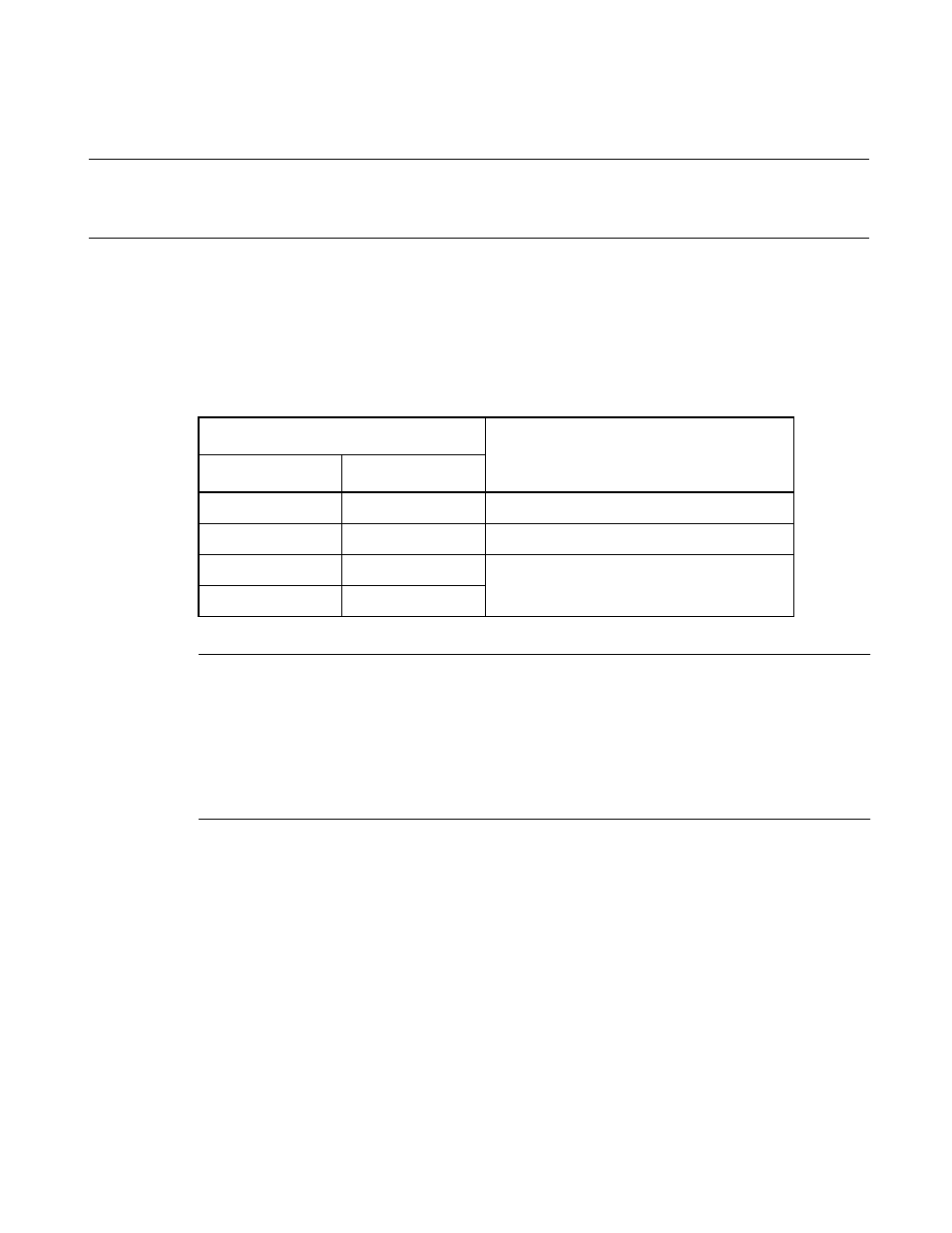

Table 8.5-2 Setting of Clock Selection Register (CKSCR) and Sleep Mode

Clock selection register (CKSCR)

Sleep mode to be switched

MCS

SCS

1

1

Main sleep mode

0

1

PLL sleep mode

1

0

Sub-sleep mode

0

0