FUJITSU F2MCTM-16LX User Manual

Page 624

608

APPENDIX

Note:

See Table B.5-1 and Table B.5-2 for information on (a) to (d) in the table.

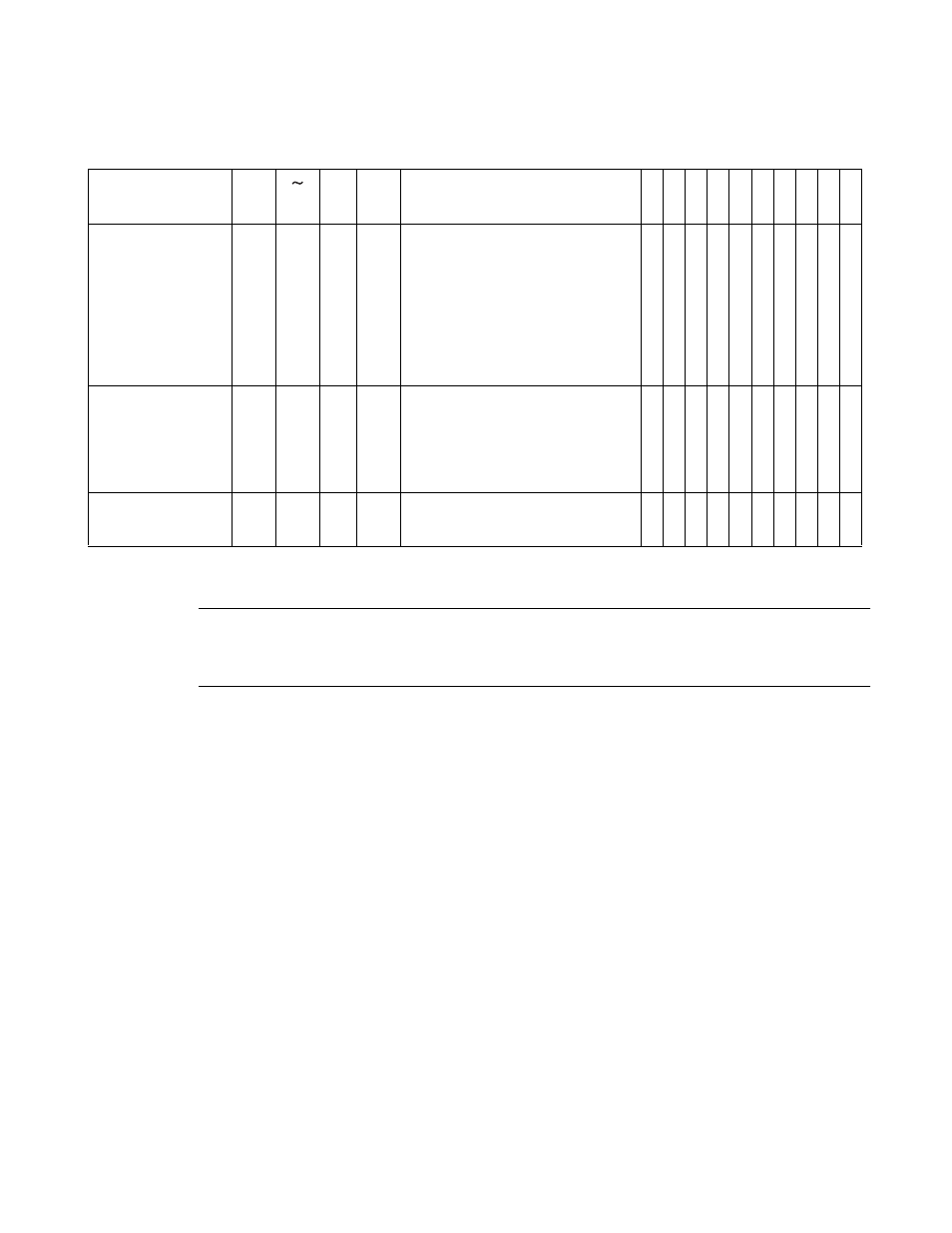

Table B.8-12 18 Shift Instructions (byte, word, long word)

Mnemonic

#

RG

B

Operation

L

H

A

H

I

S

T

N

Z

V

C

R

M

W

RORC

A

2

2

0

0

byte (A) <-- With right rotation carry

-

-

-

-

-

*

*

-

*

-

ROLC

A

2

2

0

0

byte (A) <-- With left rotation carry

-

-

-

-

-

*

*

-

*

-

RORC

ear

2

3

2

0

byte (ear) <-- With right rotation carry

-

-

-

-

-

*

*

-

*

-

RORC

eam

2+

5+(a)

0

2 x (b)

byte (eam) <-- With right rotation carry

-

-

-

-

-

*

*

-

*

*

ROLC

ear

2

3

2

0

byte (ear) <-- With left rotation carry

-

-

-

-

-

*

*

-

*

-

ROLC

eam

2+

5+(a)

0

2 x (b)

byte (eam) <-- With left rotation carry

-

-

-

-

-

*

*

-

*

*

ASR

A,R0

2

*1

1

0

byte (A) <-- Arithmetic right shift (A, 1 bit)

-

-

-

-

-

*

*

-

*

-

LSR

A,R0

2

*1

1

0

byte (A) <-- Logical right barrel shift (A, R0)

-

-

-

-

-

*

*

-

*

-

LSL

A,R0

2

*1

1

0

byte (A) <-- Logical left barrel shift (A, R0)

-

-

-

-

-

*

*

-

*

-

ASRW

A

1

2

0

0

word (A) <-- Arithmetic right shift (A, 1 bit)

-

-

-

-

*

*

*

-

*

-

LSRW

A/SHRW A

1

2

0

0

word (A) <-- Logical right shift (A, 1 bit)

-

-

-

-

*

R

*

-

*

-

LSLW

A/SHLW A

1

2

0

0

word (A) <-- Logical left shift (A, 1 bit)

-

-

-

-

-

*

*

-

*

-

ASRW

A,R0

2

*1

1

0

word (A) <-- Arithmetic right barrel shift (A, R0)

-

-

-

-

*

*

*

-

*

-

LSRW

A,R0

2

*1

1

0

word (A) <-- Logical right barrel shift (A, R0)

-

-

-

-

*

*

*

-

*

-

LSLW

A,R0

2

*1

1

0

word (A) <-- Logical left barrel shift (A, R0)

-

-

-

-

-

*

*

-

*

-

ASRL

A,R0

2

*2

1

0

long (A) <-- Arithmetic right barrel shift (A, R0)

-

-

-

-

*

*

*

-

*

-

LSRL

A,R0

2

*2

1

0

long (A) <-- Logical right barrel shift (A, R0)

-

-

-

-

*

*

*

-

*

-

LSLL

A,R0

2

*2

1

0

long (A) <-- Logical left barrel shift (A, R0)

-

-

-

-

-

*

*

-

*

-

*1: 6 when R0 is 0; otherwise, 5 + (R0)

*2: 6 when R0 is 0; otherwise, 6 + (R0)