FUJITSU F2MCTM-16LX User Manual

Page 235

219

CHAPTER 13 16-Bit I/O TIMER

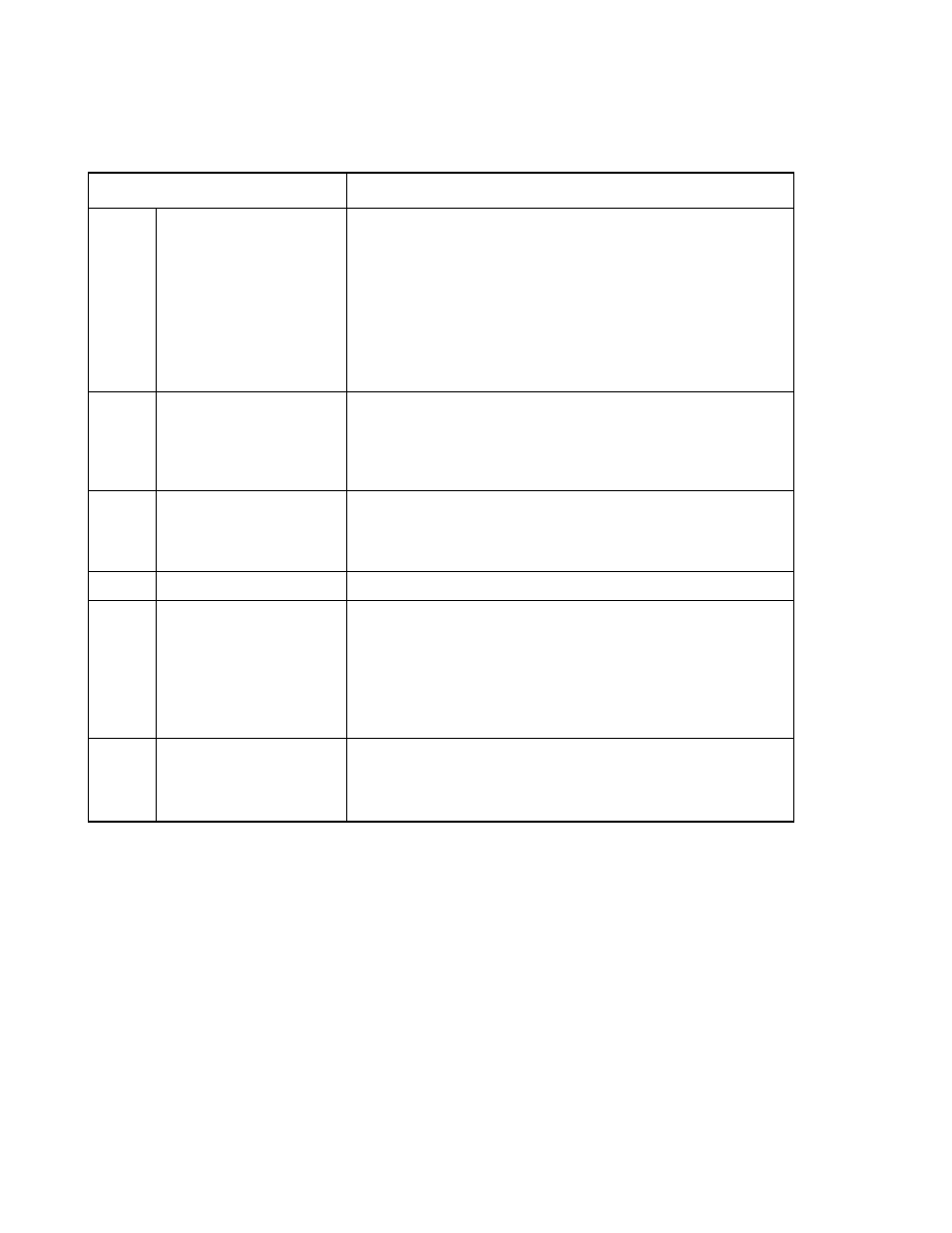

Table 13.3-3 Functions of Timer Control Status Register (Lower) (TCCSL)

Bit name

Function

bit7

IVF:

Timer overflow generation

flag bit

This bit indicates the timer overflow.

[Condition set to "1"]

Condition is set when the following is used.

• When 16-bit free-run timer overflows

[When set to "1"]

When the timer overflow interrupt request is set to enable (TCCSL:IVFE=1)

if the IVF bit is set to "1", the interrupt request is generated.

When set to "0": The bit is cleared.

When set to "1": No effect.

Read by read modify write instructions: "1" is always read.

bit6

IVFE:

Timer overflow interrupt

enable bit

This bit enables or disables the interrupt request when the IVF bit is set to

"1".

When set to "1":

When the IVF bit is set to "1", the interrupt request is

generated.

When set to "0":

The generation of the interrupt request is disabled.

bit5

STOP:

Timer operation stop bit

This bit enables or disables (stops) the operation of the 16-bit free-run timer.

When set to "0": Enable the timer operation and count up with count clock

set by the CLK2 to CLK0.

When set to "1":Stops count operation

bit4

Reserved bit

Always set this bit to "0".

bit3

CLR:

Timer clear bit

This bit clears the counter (TCDT) of the 16-bit free-run timer.

When set to "1": Clears timer data register (TCDT) to "0000

H

"

When set to "0": No effect.

Read: "0" is always read.

Note:

When clearing during stopping of the 16-bit free-run timer

(TCCSL:STOP=1), write "0000

H

" to the TCDT directly.

bit2

bit1

bit0

CLK2, CLK1, CLK0:

Count clock cycle selection

bits

These bits set the count clock to cycle of the 16-bit free-run timer.

Note:

Set the count clock cycle during stopping of the input capture operation

(ICSnm: EGn1, EGn0="00

B

" or ICSnm:EGm1, EGm0="00

B

").

n=0, 2 m=n+1