1 ppgc operation mode control register (ppgcc), Ppgc operation mode control register (ppgcc) – FUJITSU F2MCTM-16LX User Manual

Page 308

292

CHAPTER 16 8-/16-BIT PPG TIMER

16.3.1

PPGC Operation Mode Control Register (PPGCC)

The PPGC operation mode control register (PPGC0) provides the following settings for

the operation of 8-/16-bit PPG timer C:

• Enabling or disabling operation of 8-/16-bit PPG timer C

• Switching between pin functions (enabling or disabling pulse output)

• Enabling or disabling underflow interrupt

• Setting underflow interrupt request flag

This section explains the PPGCC function only. The PPGCE has the same function as

the PPGCC, and the 8-/16-bit PPPG timer C and E is set.

■

PPGC Operation Mode Control Register (PPGCC)

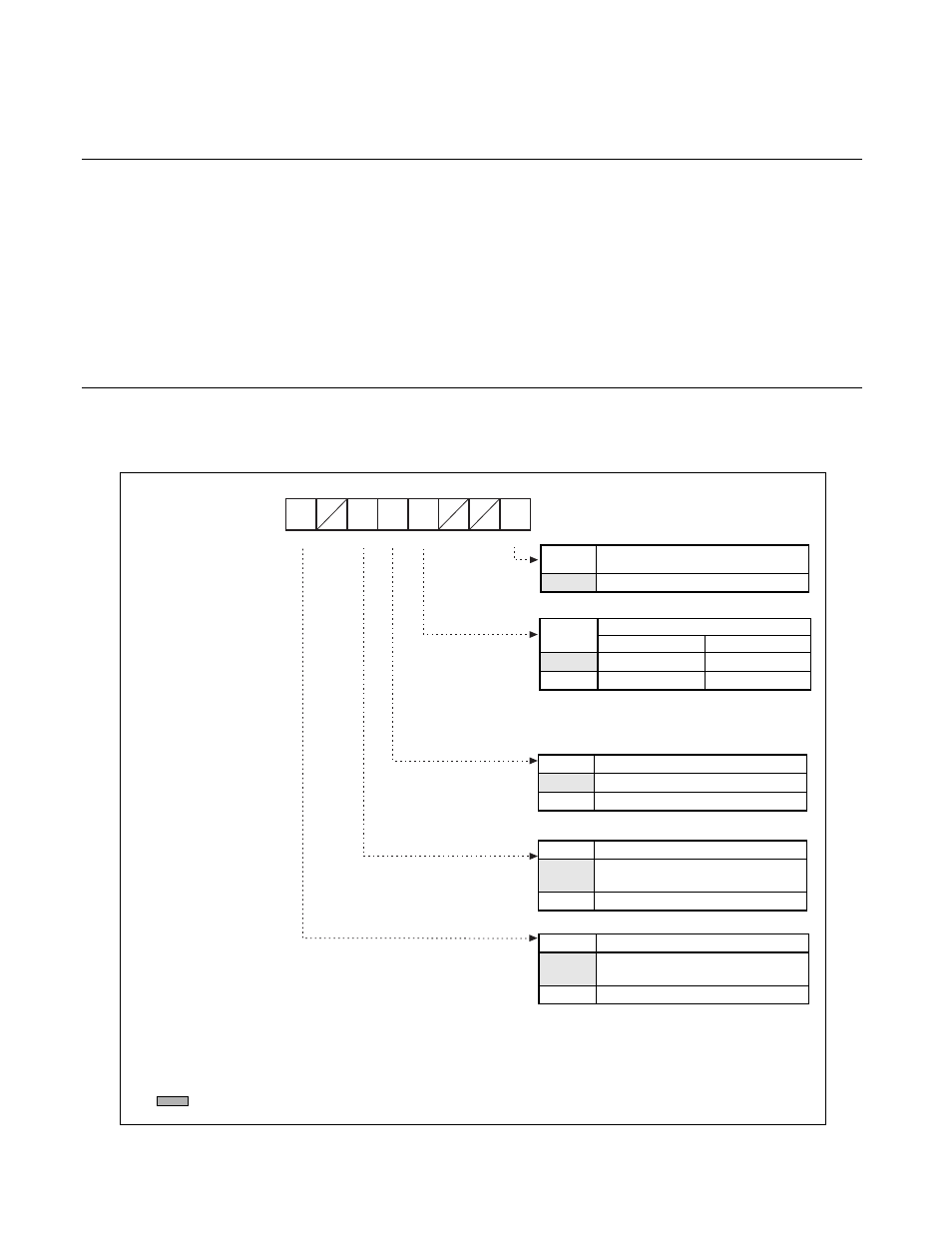

Figure 16.3-2 PPGC Operation Mode Control Register (PPGCC)

4

5

3

2

1

0

7

6

−

−

−

R/W

R/W

R/W

R/W

0

X

0

0

0

X

X

1

B

R/W

PEN0

PE0 PIE0 PUF0

Re-

served

Address:

chC

PPGCC

000048

H

Other channel:

chE

PPGCE

00004C

H

Reset value

bit 0

Re-

served

Reserved bit

1

Always set to "1"

bit 3

PUF0

Underflow generation flag bit

Read

Write

0

No underflow

Clears PUF0 bit

1

Underflow

No effect

bit 4

PIE0

Underflow interrupt enable bit

0

Interrupt request disable

1

Interrupt request enable

bit 5

PE0

PPG0 pin output enable bit

0

General-purpose I/O port

(pulse output disable)

1

PPGC output (pulse output enable)

bit 7

PEN0

PPG0 operation enable bit

0

Couting disable

(holds "L" level output)

1

Counting enable

R/W

: Read/Write

W

: Write only

X

: Indeterminate

−

: Undefined

: Reset value