4 interrupts of 8-/16-bit ppg timer, Interrupts of 8-/16-bit ppg timer – FUJITSU F2MCTM-16LX User Manual

Page 315

299

CHAPTER 16 8-/16-BIT PPG TIMER

16.4

Interrupts of 8-/16-bit PPG Timer

The 8-/16-bit PPG timer can generate an interrupt request when the PPG down counter

underflows. It also not corresponds to the EI

2

OS.

■

Interrupts of 8-/16-bit PPG Timer

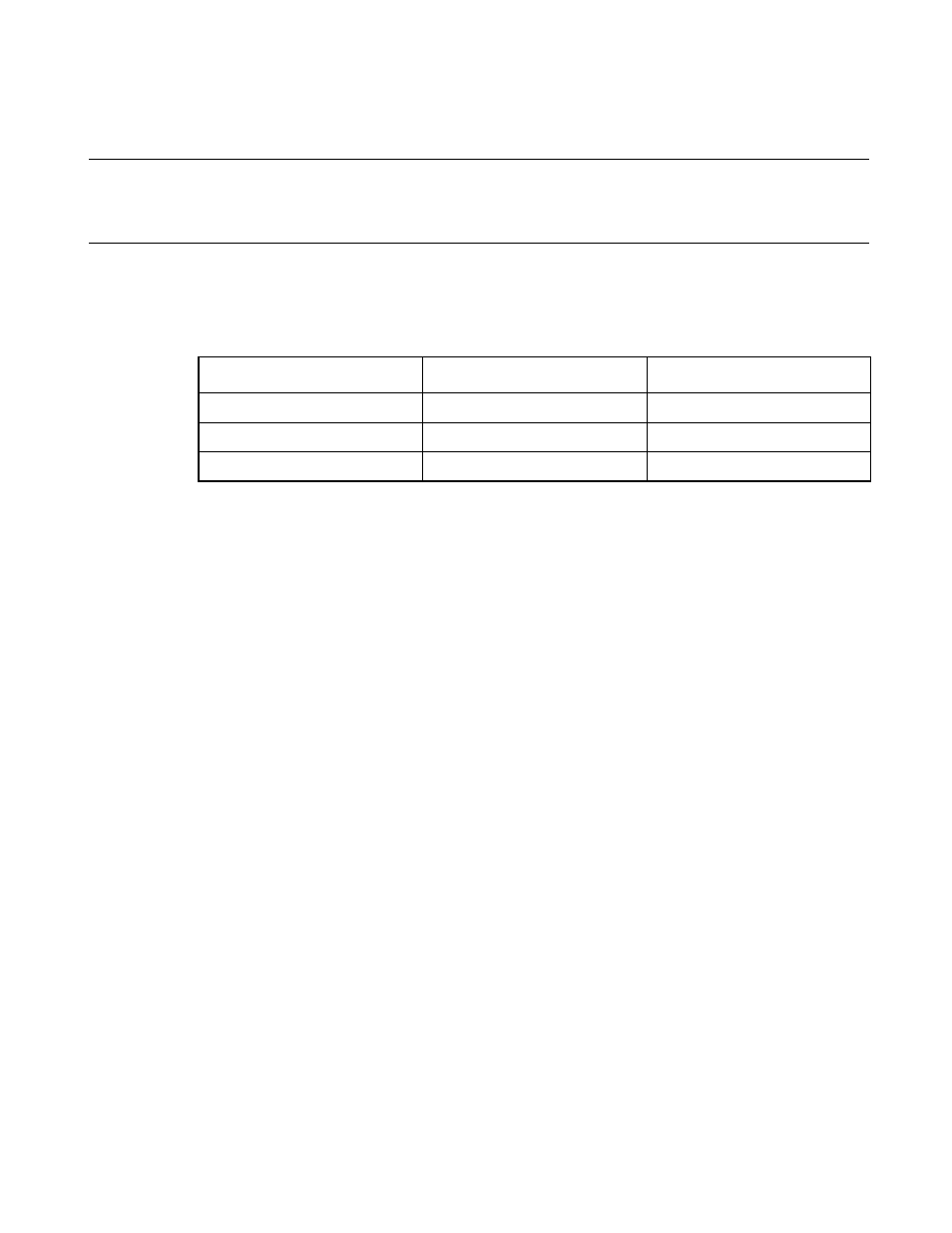

Table 16.4-1 shows the interrupt control bits and interrupt factor of the 8-/16-bit PPG timer.

Note: n = C, E m = n + 1

[8-bit PPG output 2-channel independent operation mode or 8 + 8-bit PPG output operation mode]

•

In the 8-bit PPG output 2-channel independent operation mode or the 8 + 8-bit PPG output operation

mode, the PPGn and PPGm timers can generate an interrupt independently.

•

When the value of the PPGn or PPGm down counter is decremented from "00

H

" to "FF

H

", an underflow

occurs. When an underflow occurs, the underflow generation flag bit in the channel causing an

underflow is set (PPGC

n

: PUF0=1 or PPGC

m

: PUF1=1).

•

If an interrupt request from the channel that causes an underflow is enabled (PPGC

n

: PIE0=1 or

PPGC

m

: PIE1=1), an interrupt request is generated.

[16-bit PPG output operation mode]

•

In the 16-bit PPG output operation mode, when the values of the PPGn and PPGm down counters are

decremented from "0000

H

" to "FFFF

H

", an underflow occurs. When an underflow occurs, the underflow

generation flag bits in the two channels are set at one time (PPGC

n

: PUF0=1 or PPGC

m

: PUF1=1).

•

When an underflow occurs with either of the two channel of the interrupt requests enabled (PPGC

n

:

PIE1=0, PPGC

m

: PIE1=1 or PPGC

n

: PIE0=1, PPGC

m

: PIE0=0), an interrupt request is generated.

•

To prevent duplication of interrupt requests, disable either of the two channel of the underflow interrupt

enable bits in advance (PPGC

n

: PIE0=0, PPGC

m

: PIE1=1 or PPGC

n

: PIE0=1, PPGC

m

: PIE1=0).

•

When the two channels of the underflow generation flag bits are set (PPGC

n

: PUF0=1 and PPGC

m

:

PUF1=1), clear the two channels at the same time.

■

Interrupt of 8-/16-bit PPG Timer

For details of the interrupt number, interrupt control register, and interrupt vector address, see "CHAPTER

Table 16.4-1 Interrupt Control Bits of 8-/16-bit PPG Timer

PPGn

PPGm

Interrupt request flag bit

PPGCn: PUF0

PPGCm: PUF1

Interrupt request enable bit

PPGCn: PIE0

PPGCm: PIE1

Interrupt factor

Underflow in PPGn down counter

Underflow in PPGm down counter