4 a/d setting register (adsr0/adsr1), A/d setting register (adsr0/adsr1) – FUJITSU F2MCTM-16LX User Manual

Page 368

352

CHAPTER 18 8-/10-BIT A/D CONVERTER

18.3.4

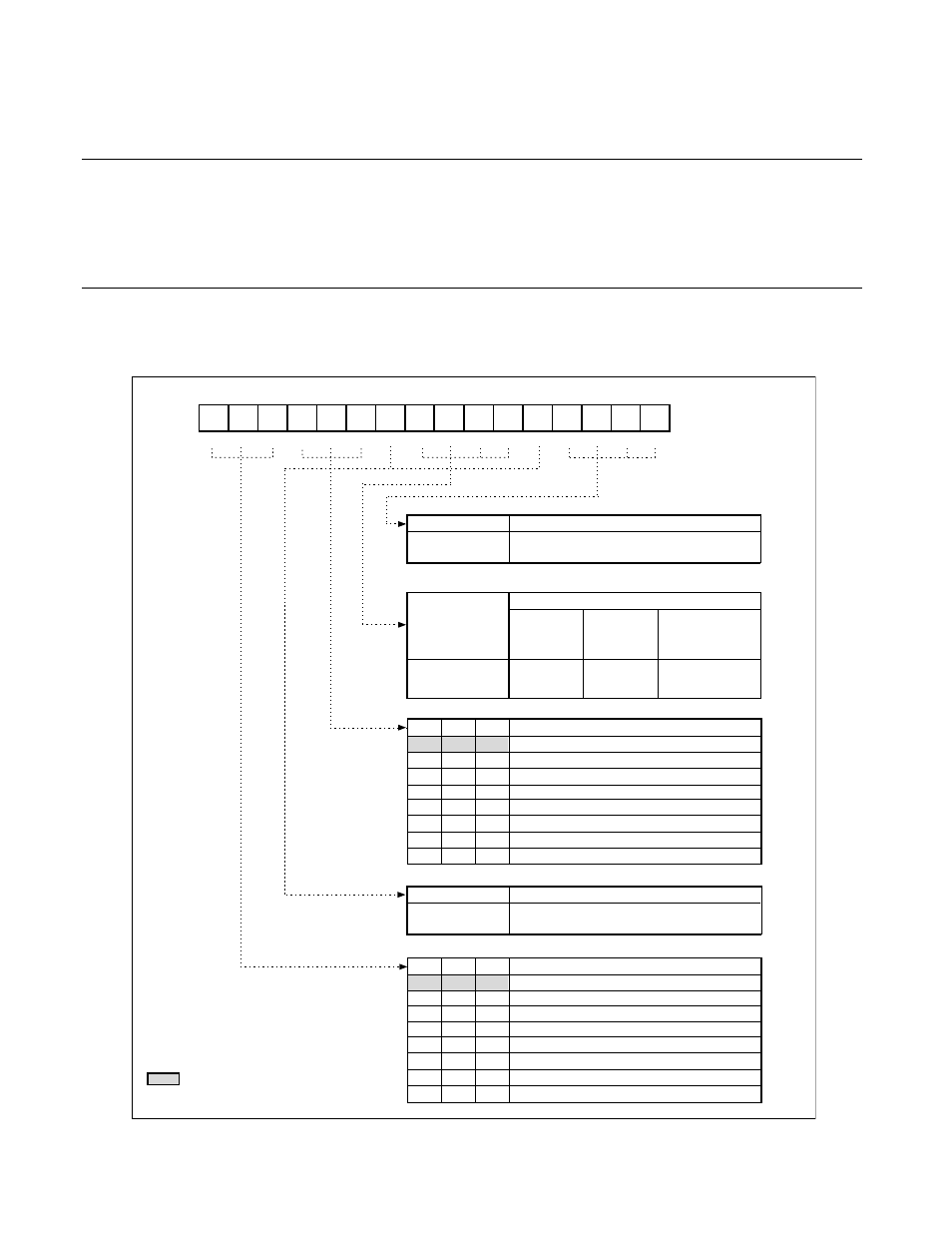

A/D Setting Register (ADSR0/ADSR1)

A/D setting register (ADSR0/ADSR1) can set as following.

• Setting of A/D conversion time (sampling time and comparing time)

• Setting of sampling channel (starting channel and end channel)

• Displaying the present sampling channels

■

A/D Setting Register (ADSR0/ADSR1)

Figure 18.3-5 A/D Setting Register (ADSR0/ADSR1)

12

13

11

10

9

8

14

15

CT2 CT1 CT0

ANS3ANS2 ANS1 ANS0

Re-

served

ANE3ANE2 ANE1 ANE0

ST2

ST1 ST0

bit12

0

0

0

0

1

1

1

1

ST2

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

ST1

bit15

bit14 bit13

ST0

bit11 bit10

R/W

φ

0

0

0

0

1

1

1

1

CT2

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

CT1

22/

φ (φ

=20 MHz: 1.1

µ

s)

33/

φ (φ

=24 MHz: 1.4

µ

s)

44/

φ (φ

=24 MHz: 1.8

µ

s)

66/

φ (φ

=24 MHz: 2.75

µ

s)

88/

φ (φ

= 8 MHz:11.0

µ

s)

132/

φ (φ

=16 MHz: 8.25

µ

s)

176/

φ (φ

=20 MHz: 8.8

µ

s)

264/

φ (φ

=24 MHz:11.0

µ

s)

4/

φ (φ

= 8 MHz:0.5

µ

s)

6/

φ (φ

= 8 MHz:0.75

µ

s)

8/

φ (φ

=16 MHz:0.5

µ

s)

12/

φ (φ

=24 MHz:0.5

µ

s)

24/

φ (φ

= 8 MHz:3.0

µ

s)

36/

φ (φ

=16 MHz:2.25

µ

s)

48/

φ (φ

=16 MHz:3.0

µ

s)

128/

φ (φ

=24 MHz:5.3

µ

s)

CT0

00006C

H

Address

Reset value

0000000000000000

B

4

5

3

2

1

0

6

7

R/W

R/W

R/W

R/W

R/W R/W

R/W

R/W

R/W

R/W R/W

R/W

R/W

R/W

R/W

R/W

ANE3 to ANE0

A/D conversion end channel select bit

AN15 pin to AN0 pin

AN15 pin

to AN0 pin

bit3 to bit0

bit8 to bit5

Channel

number

in converting

Read at pausing

in pause-

conversion mode

Converted channel

number immediately

before

ANS3 to ANS0

1111

B

to 0000

B

(reset value:0000

B

)

1111

B

to 0000

B

(reset value:0000

B

)

Reserved

bit9,bit4

0

: Read/Write

: Machine clock

: Reset value

Sampling time select bit

Reserved bit

Always write 0 to this bit.

Reading value is always 0.

Comparing time select bit

A/D conversion start channel select bit

Write

(state in not

starting)

Read

in converting

Re-

served