B.6 effective address field, Effective address field – FUJITSU F2MCTM-16LX User Manual

Page 612

596

APPENDIX

B.6

Effective address field

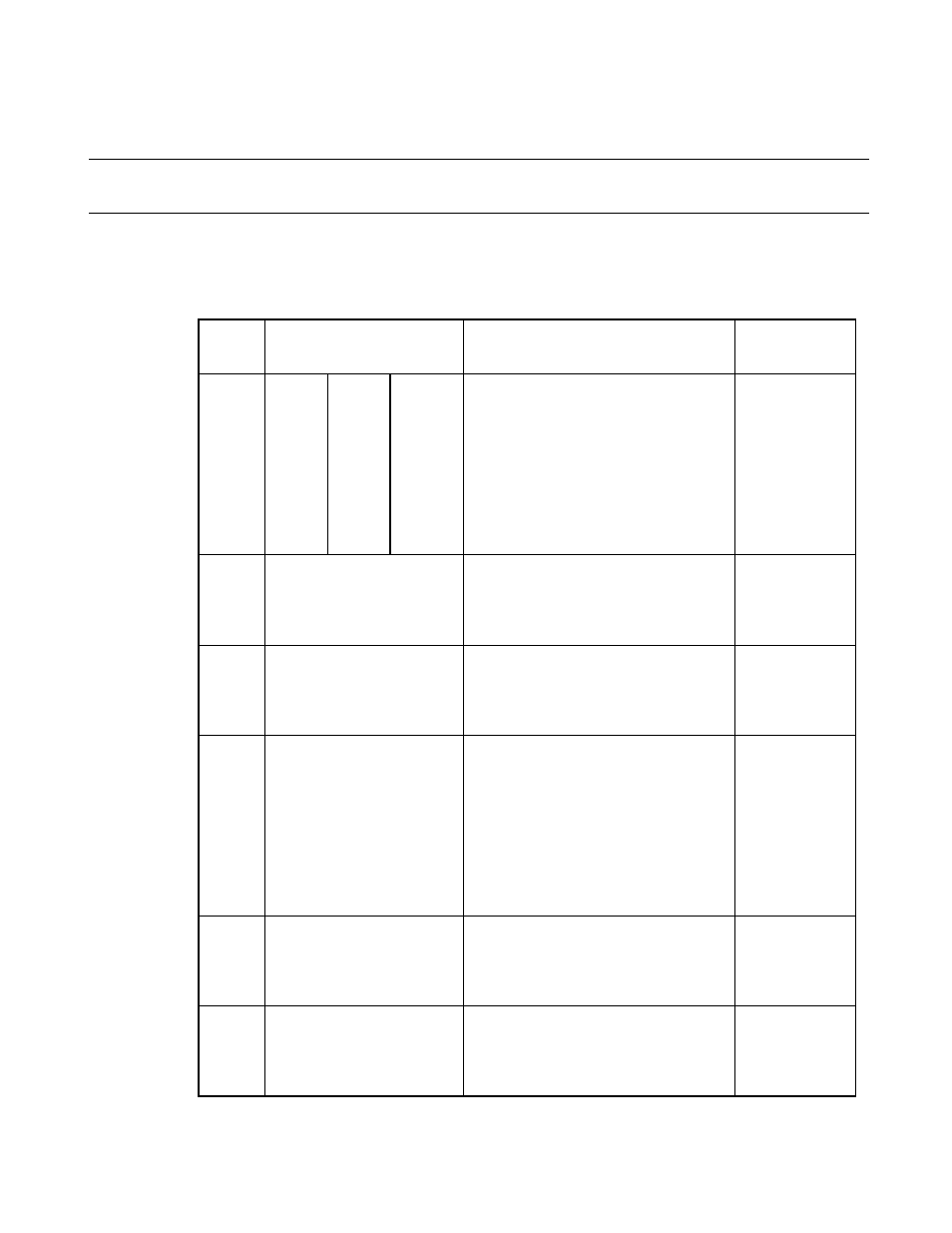

Table B.6-1 shows the effective address field.

■

Effective Address Field

Table B.6-1 Effective Address Field

Code

Representation

Address format

Byte count of

extended address

part

*

00

R0

RW0

RL0

Register direct: Individual parts

correspond to the byte, word, and long

word types in order from the left.

-

01

R1

RW1

(RL0)

02

R2

RW2

RL1

03

R3

RW3

(RL1)

04

R4

RW4

RL2

05

R5

RW5

(RL2)

06

R6

RW6

RL3

07

R7

RW7

(RL3)

08

@RW0

Register indirect

0

09

@RW1

0A

@RW2

0B

@RW3

0C

@RW0+

Register indirect with post increment

0

0D

@RW1+

0E

@RW2+

0F

@RW3+

10

@RW0+disp8

Register indirect with 8-bit displacement

1

11

@RW1+disp8

12

@RW2+disp8

13

@RW3+disp8

14

@RW4+disp8

15

@RW5+disp8

16

@RW6+disp8

17

@RW7+disp8

18

@RW0+disp16

Register indirect with 16-bit

displacement

2

19

@RW1+disp16

1A

@RW2+disp16

1B

@RW3+disp16

1C

@RW0+RW7

Register indirect with index

0

1D

@RW1+RW7

Register indirect with index

0

1E

@PC+disp16

PC indirect with 16-bit displacement

2

1F

addr16

Direct address

2

*: Each byte count of the extended address part applies to + in the # (byte count) column in "B.8 F

16LX Instruction List". For the meaning of "#", see "B.7 How to Read the Instruction List".