FUJITSU F2MCTM-16LX User Manual

Page 625

609

APPENDIX B Instructions

Note:

See Table B.5-1 and Table B.5-2 for information on (a) to (d) in the table.

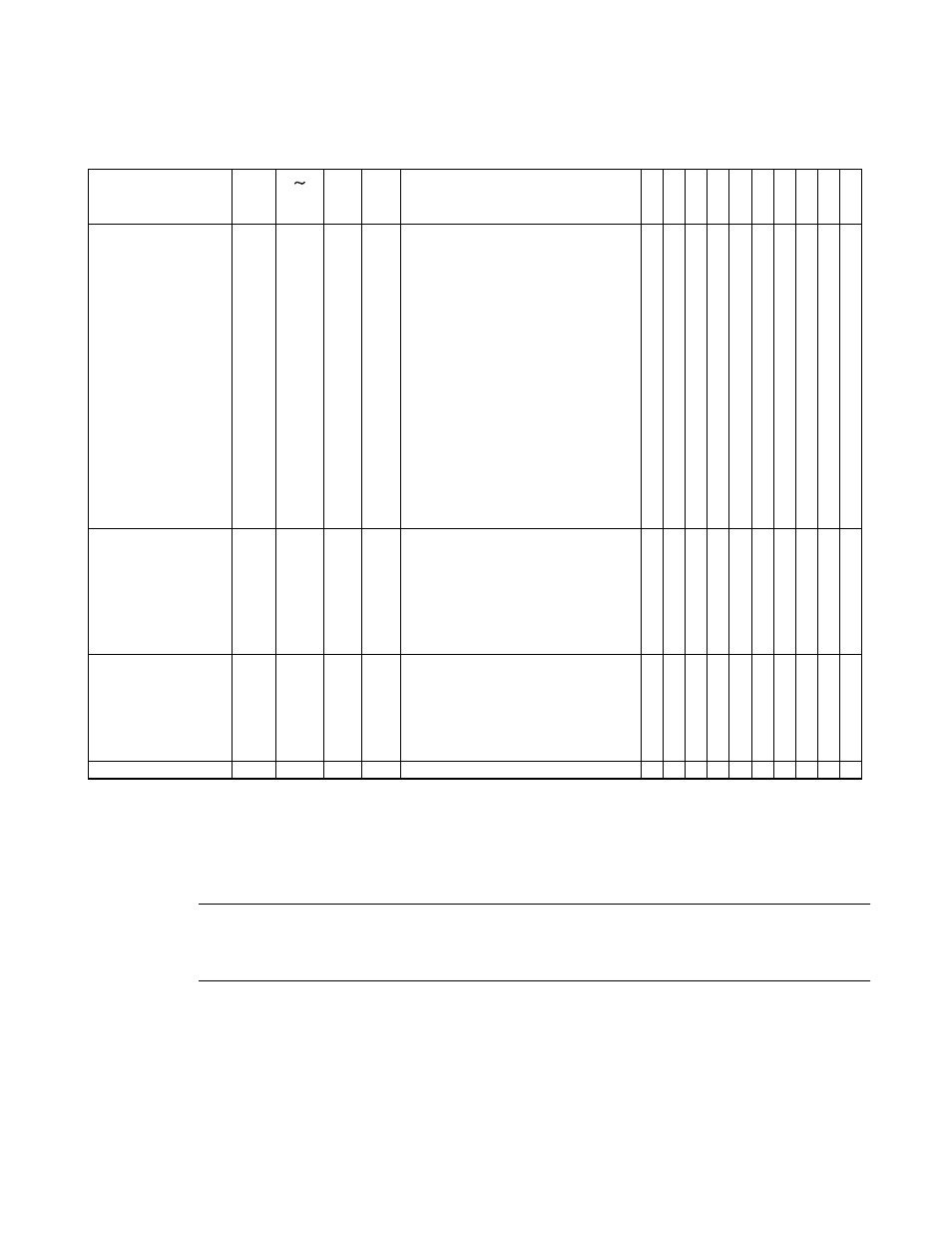

Table B.8-13 31 Branch 1 Instructions

Mnemonic

#

RG

B

Operation

L

H

A

H

I

S

T

N

Z

V

C

R

M

W

BZ/BEQ

rel

2

*1

0

0

Branch on (Z) = 1

-

-

-

-

-

-

-

-

-

-

BNZ/BNE

rel

2

*1

0

0

Branch on (Z) = 0

-

-

-

-

-

-

-

-

-

-

BC/BLO

rel

2

*1

0

0

Branch on (C) = 1

-

-

-

-

-

-

-

-

-

-

BNC/BHS

rel

2

*1

0

0

Branch on (C) = 0

-

-

-

-

-

-

-

-

-

-

BN

rel

2

*1

0

0

Branch on (N) = 1

-

-

-

-

-

-

-

-

-

-

BP

rel

2

*1

0

0

Branch on (N) = 0

-

-

-

-

-

-

-

-

-

-

BV

rel

2

*1

0

0

Branch on (V) = 1

-

-

-

-

-

-

-

-

-

-

BNV

rel

2

*1

0

0

Branch on (V) = 0

-

-

-

-

-

-

-

-

-

-

BT

rel

2

*1

0

0

Branch on (T) = 1

-

-

-

-

-

-

-

-

-

-

BNT

rel

2

*1

0

0

Branch on (T) = 0

-

-

-

-

-

-

-

-

-

-

BLT

rel

2

*1

0

0

Branch on (V) nor (N) = 1

-

-

-

-

-

-

-

-

-

-

BGE

rel

2

*1

0

0

Branch on (V) nor (N) = 0

-

-

-

-

-

-

-

-

-

-

BLE

rel

2

*1

0

0

Branch on ((V) xor (N)) or (Z) = 1

-

-

-

-

-

-

-

-

-

-

BGT

rel

2

*1

0

0

Branch on ((V) xor (N)) or (Z) = 0

-

-

-

-

-

-

-

-

-

-

BLS

rel

2

*1

0

0

Branch on (C) or (Z) = 1

-

-

-

-

-

-

-

-

-

-

BHI

rel

2

*1

0

0

Branch on (C) or (Z) = 0

-

-

-

-

-

-

-

-

-

-

BRA

rel

2

*1

0

0

Unconditional branch

-

-

-

-

-

-

-

-

-

-

JMP

@A

1

2

0

0

word (PC) <-- (A)

-

-

-

-

-

-

-

-

-

-

JMP

addr16

3

3

0

0

word (PC) <-- addr16

-

-

-

-

-

-

-

-

-

-

JMP

@ear

2

3

1

0

word (PC) <-- (ear)

-

-

-

-

-

-

-

-

-

-

JMP

@eam

2+

4+(a)

0

(c)

word (PC) <-- (eam)

-

-

-

-

-

-

-

-

-

-

JMPP

@ear *3

2

5

2

0

word (PC) <-- (ear), (PCB) <-- (ear+2)

-

-

-

-

-

-

-

-

-

-

JMPP

@eam *3

2+

6+(a)

0

(d)

word (PC) <-- (eam), (PCB) <-- (eam+2)

-

-

-

-

-

-

-

-

-

-

JMPP

addr24

4

4

0

0

word (PC) <-- ad24 0-15, (PCB) <-- ad24 16-23

-

-

-

-

-

-

-

-

-

-

CALL

@ear *4

2

6

1

(c)

word (PC) <-- (ear)

-

-

-

-

-

-

-

-

-

-

CALL

addr16 *5

2+

7+(a)

0

2 x (c)

word (PC) <-- (eam)

-

-

-

-

-

-

-

-

-

-

CALL

@eam *4

3

6

0

(c)

word (PC) <-- addr16

-

-

-

-

-

-

-

-

-

-

CALLV

#vct4 *5

1

7

0

2 x (c)

Vector call instruction

-

-

-

-

-

-

-

-

-

-

CALLP

@ear *6

2

10

2

2 x (c)

word (PC) <-- (ear)0-15, (PCB) <-- (ear)16-23

-

-

-

-

-

-

-

-

-

-

CALLP

@eam *6

2+

11+(a)

0

*2

word (PC) <-- (eam)0-15, (PCB) <-- (eam)16-23

-

-

-

-

-

-

-

-

-

-

CALLP

addr24 *7

4

10

0

2 x (c)

word (PC) <-- addr0-15, (PCB) <-- addr16-23

-

-

-

-

-

-

-

-

-

-

*1: 4 when a branch is made; otherwise, 3

*2: 3 x (c) + (b)

*3: Read (word) of branch destination address

*4: W: Save to stack (word) R: Read (word) of branch destination address

*5: Save to stack (word)

*6: W: Save to stack (long word), R: Read (long word) of branch destination address

*7: Save to stack (long word)