B.4 indirect addressing, Indirect addressing – FUJITSU F2MCTM-16LX User Manual

Page 602

586

APPENDIX

B.4

Indirect Addressing

In indirect addressing mode, an address is specified indirectly by the address data of an

operand.

■

Indirect Addressing

●

Register indirect addressing (@RWj j = 0 to 3)

Memory is accessed using the contents of general-purpose register RWj as an address. Address bits 16 to

23 are indicated by the data bank register (DTB) when RW0 or RW1 is used, system stack bank register

(SSB) or user stack bank register (USB) when RW3 is used, or additional data bank register (ADB) when

RW2 is used.

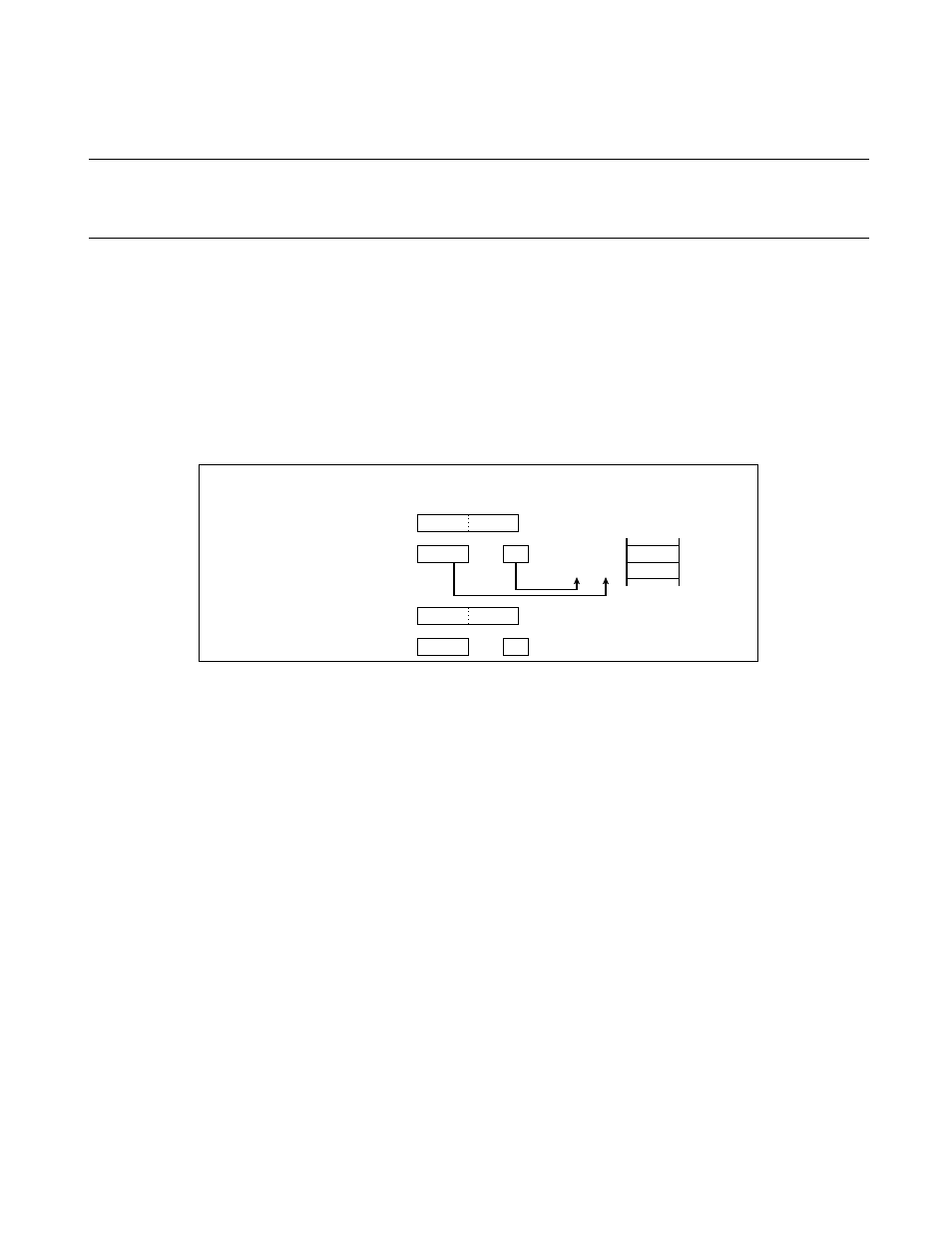

Figure B.4-1 Example of Register Indirect Addressing (@RWj j = 0 to 3)

●

Register indirect addressing with post increment (@RWj+ j = 0 to 3)

Memory is accessed using the contents of general-purpose register RWj as an address. After operand

operation, RWj is incremented by the operand size (1 for a byte, 2 for a word, or 4 for a long word).

Address bits 16 to 23 are indicated by the data bank register (DTB) when RW0 or RW1 is used, system

stack bank register (SSB) or user stack bank register (USB) when RW3 is used, or additional data bank

register (ADB) when RW2 is used.

If the post increment results in the address of the register that specifies the increment, the incremented

value is referenced after that. In this case, if the next instruction is a write instruction, priority is given to

writing by an instruction and, therefore, the register that would be incremented becomes write data.

MOVW A, @RW1

0 7 1 6

A

D 3 0 F

2 5 3 4

RW1

F F

E E

2 5 3 4

A

D 3 0 F

F F E E

RW1

7 8

DTB

7 8

DTB

78D310H

78D30FH

Before execution

After execution

Memory space

(This instruction reads data by register indirect addressing and stores it in A.)