FUJITSU F2MCTM-16LX User Manual

Page 238

222

CHAPTER 13 16-Bit I/O TIMER

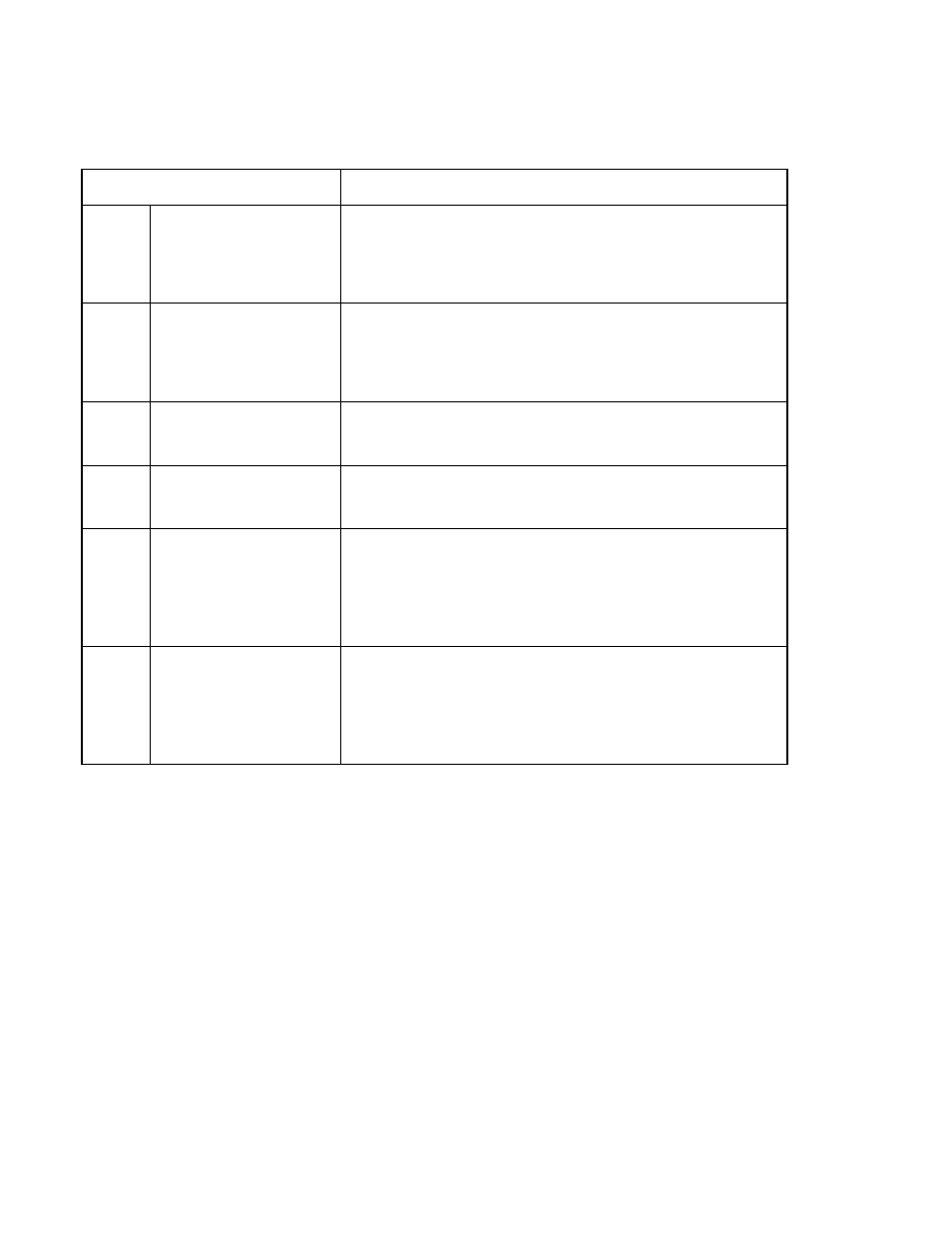

Table 13.3-4 Functions of Input Capture Control Status Register (ICS)

Bit name

Function

bit7

ICPm:

Valid edge detection flag bit m

This bit is set to "1" when the valid edge is detected by the INm pin.

When the interrupt request of the input capture m is set to enable

(ICSnm:ICEm=1), if the ICPm bit is set, the interrupt request is generated.

When set to "0": The bit is cleared.

When set to "1": No effect.

bit6

ICPn:

Valid edge detection flag bit n

This bit is set to "1" when the valid edge is detected by the INn pin.

When the interrupt request of the input capture m is set to enable

(ICSnm:ICEn=1), if the ICPn bit is set, the interrupt request is generated.

When set to "0": The bit is cleared.

When set to "1": No effect.

bit5

ICEm:

Capture interrupt enable bit m

This bit enables or disables the interrupt request of the input capture m.

When set to "1": When the valid edge detection flag bit m is set to "1"

(ICSnm: ICPm=1), the interrupt request is generated.

bit4

ICEn:

Capture interrupt enable bit n

This bit enables or disables the interrupt request of the input capture n.

When set to "1": When the valid edge detection flag bit n is set to "1"

(ICSnm: ICPn=1), the interrupt request is generated.

bit3

bit2

EGm1, EGm0:

Edge select bits m

For the input capture register m, the trigger edge of the capture operation is

set.

• Setting of the trigger edge is used to specify enable and stop of the opera-

tion.

When set to "00

B

": The operation of input capture is disabled and no edge

is detected.

bit1

bit0

EGn1, EGn0:

Edge select bits n

For the input capture register n, the trigger edge of the capture operation is

set.

• Setting of the trigger edge is used to specify enable and stop of the opera-

tion.

When set to "00

B

": The operation of input capture is disabled and no edge

is detected.

n = 0, 2 m = n + 1