FUJITSU F2MCTM-16LX User Manual

Page 604

588

APPENDIX

●

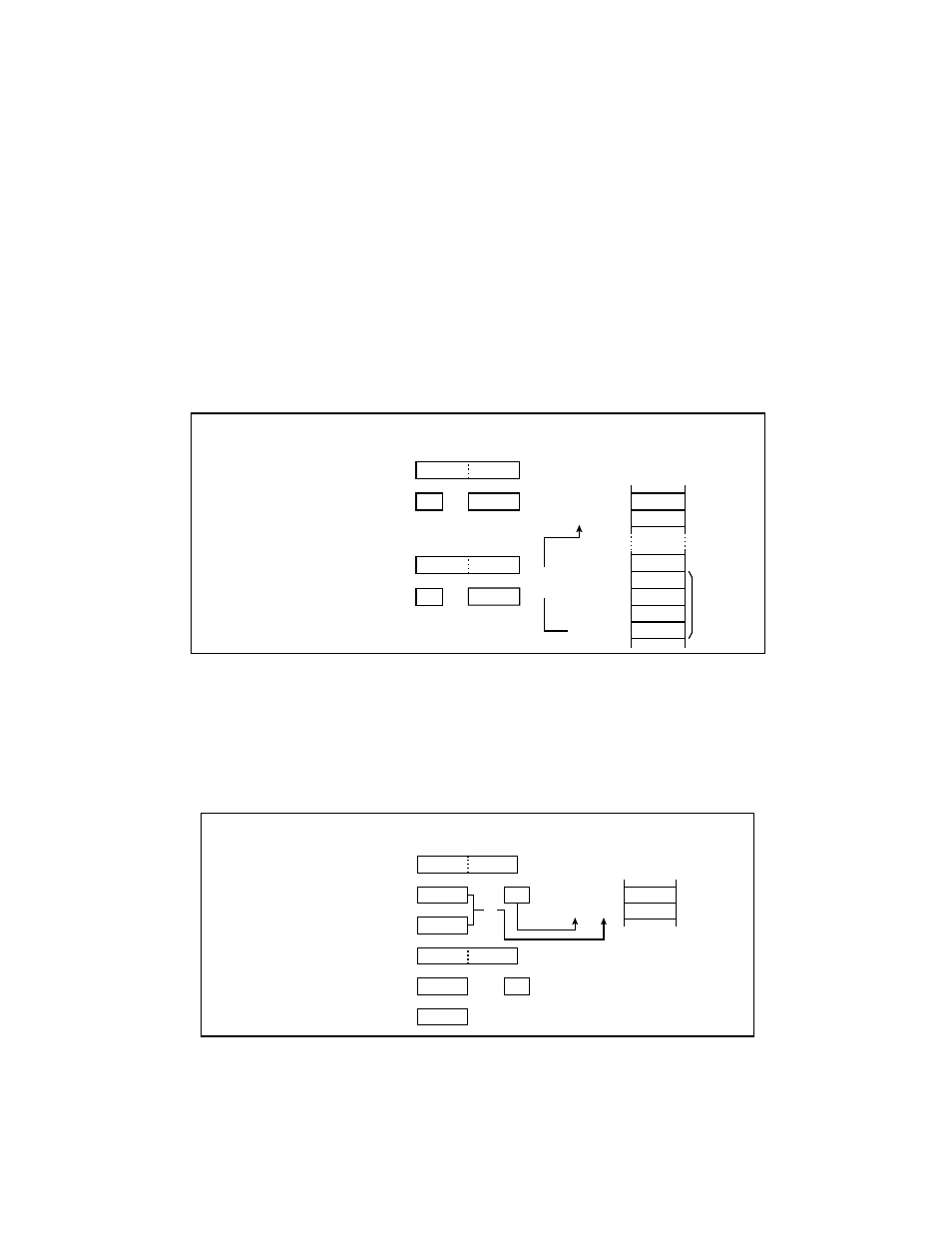

Program counter indirect addressing with offset (@PC + disp16)

Memory is accessed using the address indicated by (instruction address + 4 + disp16). The offset is one

word long. Address bits 16 to 23 are specified by the program bank register (PCB). Note that the operand

address of each of the following instructions is not deemed to be (next instruction address + disp16):

•

DBNZ eam, rel

•

DWBNZ eam, rel

•

CBNE eam, #imm8, rel

•

CWBNE eam, #imm16, rel

•

MOV eam, #imm8

•

MOVW eam, #imm16

Figure B.4-5 Example of Program Counter Indirect Addressing with Offset (@PC + disp16)

●

Register indirect addressing with base index (@RW0 + RW7, @RW1 + RW7)

Memory is accessed using the address determined by adding RW0 or RW1 to the contents of general-

purpose register RW7. Address bits 16 to 23 are indicated by the data bank register (DTB).

Figure B.4-6 Example of Register Indirect Addressing with Base Index (@RW0 + RW7, @RW1 + RW7)

MOVW A, @PC+20H

0 7 1 6

A

2 5 3 4

C 5

PCB

C 5

F F

E E

0 0

2 0

MOVW

A, @PC+20H

2 5 3 4

A

F F E E

PCB

C5457BH

C5457AH

C54559H

C54558H

9 E

7 3

C54557H

C54556H

C5455AH

+20H

+4

4 5 5 6

PC

4 5 5 A

PC

Before execution

After execution

Memory space

(This instruction reads data by program counter indirect addressing with a

offset and stores it in A.)

MOVW A, @RW1+RW7

0 7 1 6

A

D 3 0 F

2 5 3 4

RW1

F F

E E

2 5 3 4

A

D 3 0 F

F F E E

RW1

0 1 0 1

RW7

7 8

DTB

0 1 0 1

RW7

7 8

DTB

78D411H

78D410H

+

Before execution

After execution

Memory space

(This instruction reads data by register indirect addressing with a

base index and stores it in A.)