Operation in event count mode – FUJITSU F2MCTM-16LX User Manual

Page 277

261

CHAPTER 14 16-BIT RELOAD TIMER

■

Operation in Event Count Mode

The operation of the 16-bit reload timer is enabled by setting the timer operation enable bit in the timer

control status register (TMCSR:CNTE) to 1. When the software trigger bit in the timer control status

register (TMCSR:TRG) is set to 1, the 16-bit reload timer is started. When the 16-bit reload timer is started,

the value set in the 16-bit reload register (TMRLR) is reloaded to the 16-bit timer register (TMR), starting

the TMR count operation. After the 16-bit reload timer is started, the edge of the external event clock input

to the TIN pin is detected to perform the TMR count operation.

•

By setting the operating mode select bits in the timer control status register (TMCSR:MOD2 to MOD0),

the detected edge can be selected from the rising edge, falling edge, and both edges.

Note:

The level width of the external event clock to be inputted to the TIN pin should be 4 T (T: machine

cycles) or more.

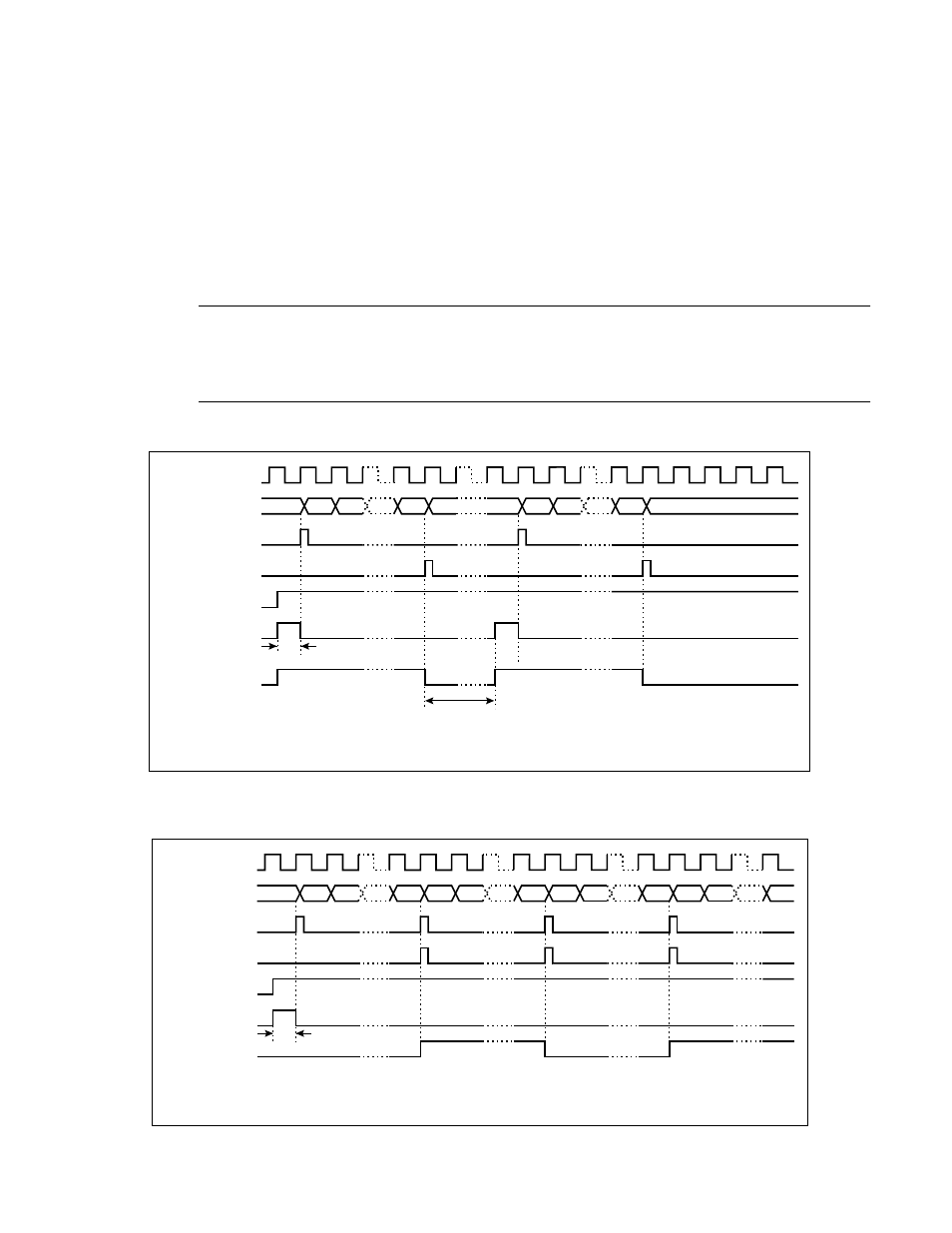

Figure 14.5-10 Count Operation in Event Count Mode (One-shot Mode)

Figure 14.5-11 Count Operation in Event Count Mode (Reload Mode)

Reload data

0000

H

T

*

-1

FFFF

H

Reload data

0000

H

-1

FFFF

H

Counter

Data load signal

UF bit

CNTE bit

TOT pin

T : Machine cycle

* : It takes 1 T time to load data of reload register from trigger input.

Start trigger input wait

TRG bit

TIN pin

Reload data

0000

H

Reload data

0000

H

Reload data

0000

H

Reload data

T

*

-1

-1

-1

-1

Counter

Data load signal

UF bit

CNTE bit

TIN pin

TOT pin

T : Machine cycle

* : It takes 1 T time to load data of reload register from trigger input.

TRG bit