Delta DVP-ES2 User Manual

Page 261

3 . I n s t r u c t i o n S e t

3 - 1 4 5

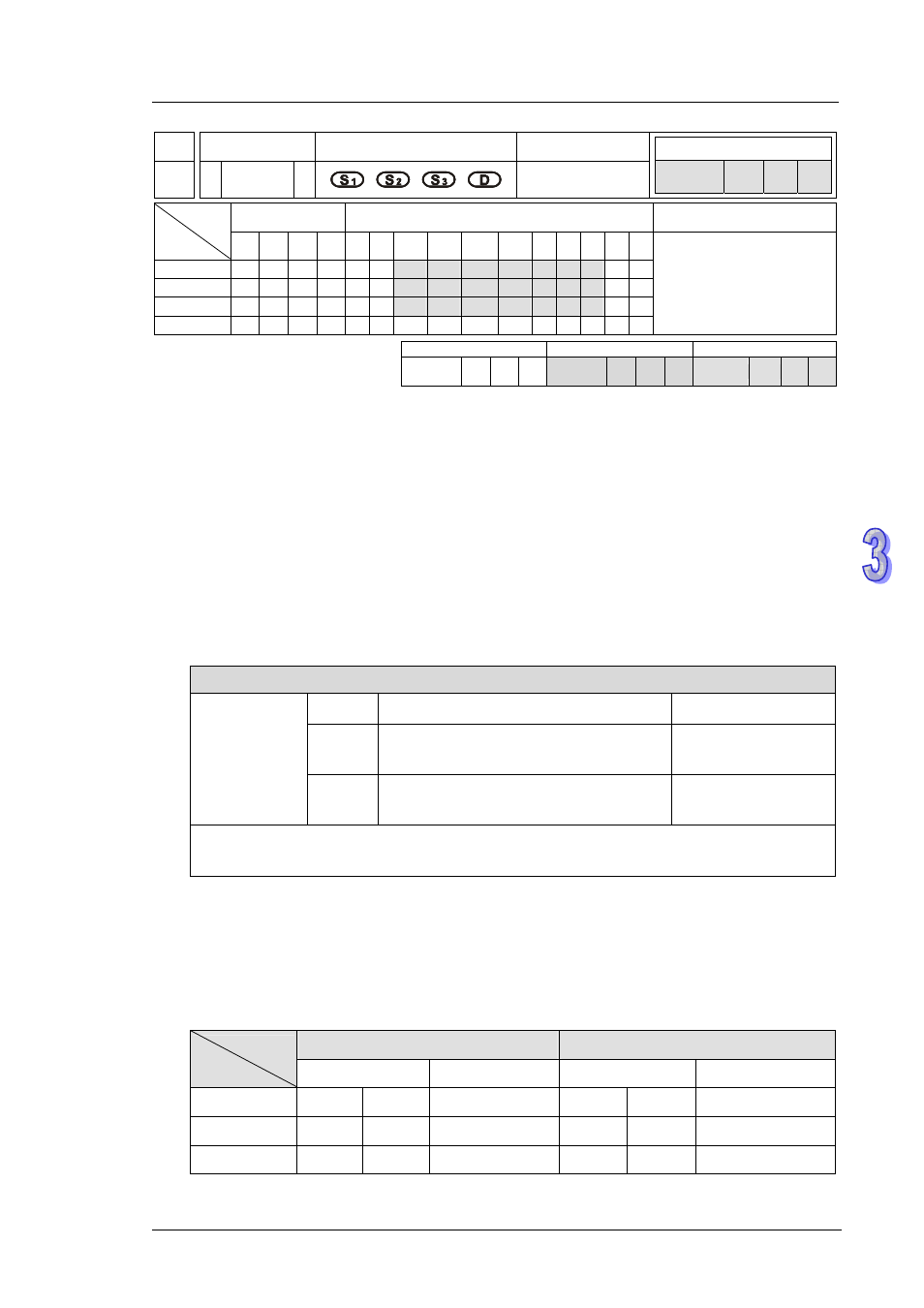

API Mnemonic

Operands

Function

59

D PLSR

Pulse Ramp

Controllers

ES2/EX2 SS2 SA2

SE

SX2

Bit Devices

Word devices

Program Steps

Type

OP

X Y

M S K H KnX KnY KnM KnS T C D E F

S

1

* *

*

*

*

*

*

*

*

*

*

S

2

* *

*

*

*

*

*

*

*

*

*

S

3

* *

*

*

*

*

*

*

*

*

*

D

*

PLSR: 9 steps

DPLSR: 17 steps

PULSE 16-bit 32-bit

ES2/EX2 SS2

SA2

SE

SX2 ES2/EX2 SS2

SA2

SE

SX2 ES2/EX2 SS2

SA2

SE

SX2

Operands:

S

1

: Maximum frequency (Hz) S

2

: Number of pulses S

3

: Ramp up/down time (ms)

D: Pulse output device (Y0, Y1, Y2 and Y3 are available) (DVP-SE does not support Y1 and Y3.)

Explanations:

52. PLSR instruction performs a frequency ramp up/down process when positioning. Speed ramp

up process is activated between static status to the target speed. Pulse output persists in

target speed before getting close to target position. When target position is near, speed ramp

down process executes, and pulse output stops when target position is achieved.

53. Set range of S

1

pulse output frequency:

Range of S

1

pulse output frequency:

Output

Y0, Y2

Y1, Y3

16-bit

SS2: 6~10,000Hz

ES2/EX2/SA2/SX2/SE: 6~32,767Hz

6~10,000Hz

Output

frequency:

32-bit

SS2: 6~10,000Hz

ES2/EX2/SA2/SX2/SE: 0~100,000Hz

6~10,000Hz

If frequency smaller than 6Hz is specified, PLC will output 6Hz.

If frequency bigger than max frequency is specified, PLC will output with max frequency.

54. When output device is specified with Y0, Y2, the start/end frequency of Y0 is set by D1340 and

start/end frequency of Y2 is set by D1352.

55. When output device is specified with Y1, Y3, the start/end frequency is 0Hz.

56. When D1220/D1221 = K1 or K2, positive/negative sign of S

2

denotes pulse output direction.

57. PLSR instruction supports two modes of pulse output as below list.

D1220

D1221

Mode

Output

K0 K1 K0 K1

Y0 Pulse

Pulse

Y1

Pulse

Dir

Y2

Pulse

Pulse