Delta DVP-ES2 User Manual

Page 246

D V P - E S 2 / E X 2 / S S 2 / S A2 / S X 2 / S E O p e r a t i o n M a n u a l - P r o g r a m m i n g

3 - 1 3 0

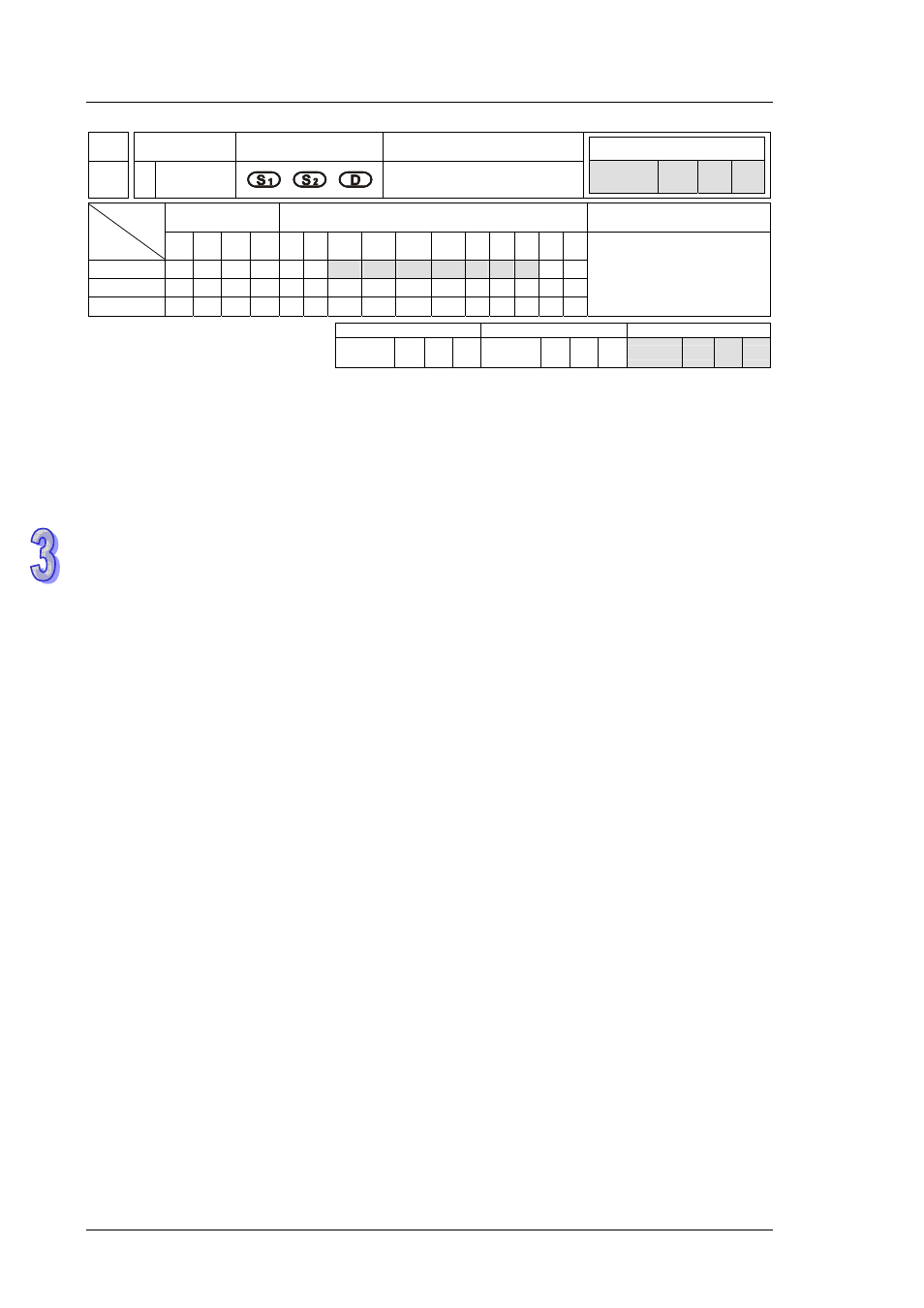

API Mnemonic

Operands

Function

54

D HSCR

High Speed Counter

Reset

Controllers

ES2/EX2 SS2 SA2

SE

SX2

Bit Devices

Word devices

Program Steps

Type

OP

X Y M S K H

KnX

KnY KnM KnS T C D E F

S

1

*

* *

*

*

*

*

*

*

*

S

2

*

D

* * *

*

DHSCR: 13 steps

PULSE 16-bit 32-bit

ES2/EX2 SS2

SA2

SE

SX2 ES2/EX2 SS2

SA2

SE

SX2 ES2/EX2 SS2

SA2

SE

SX2

Operands:

S

1

: Comparative value S

2

: No. of high speed counter D: Comparison result

Explanations:

1.

DHSCR compares the current value of the counter S

2

against a compare value S

1

. When the

counters current value changes to a value equal to S

1

, then device D is reset to OFF. Once

reset, even if the compare result is no longer unequal, D will still be OFF.

2. If

D is specified as Y0~Y3 in this instruction, the compare result will immediately output to the

external outputs Y0~Y3 (reset the designated Y). However, other Y outputs will still be updated

till the end of program (delay for one scan cycle). Also, M and S devices, not affected by the

program scan time, will be immediately updated as well.

3. Operand

D can be specified with high speed counters C232~C254 (SS2/SA2/SE does not

support C232) the same as S

2. .

4.

High speed counters include software high speed counters and hardware high speed counters.

In addtiion, there are also two types of comparators including software comparators and

hardware comparators. For detailed explanations of high speed counters please refer to

section 2.9 in this manual.

5.

For explanations on software counters and hardware counters, please refer to API53 DHSCS.

6.

For program examples, please refer to Program Example1 and 2 in API53 DHSCS.