Delta DVP-ES2 User Manual

Page 211

3 . I n s t r u c t i o n S e t

3 - 9 5

API Mnemonic

Operands

Function

34

SFTR P

Bit Shift Right

Controllers

ES2/EX2 SS2

SA2

SE

SX2

Bit Devices

Word devices

Program Steps

Type

OP

X Y

M S K H KnX KnY KnM KnS T C D E F

S

*

*

*

*

D

*

*

*

n

1

* *

n

2

* *

SFTR, SFTRP: 9 steps

PULSE 16-bit 32-bit

ES2/EX2 SS2

SA2

SE

SX2 ES2/EX2 SS2

SA2

SE

SX2 ES2/EX2 SS2

SA2

SE

SX2

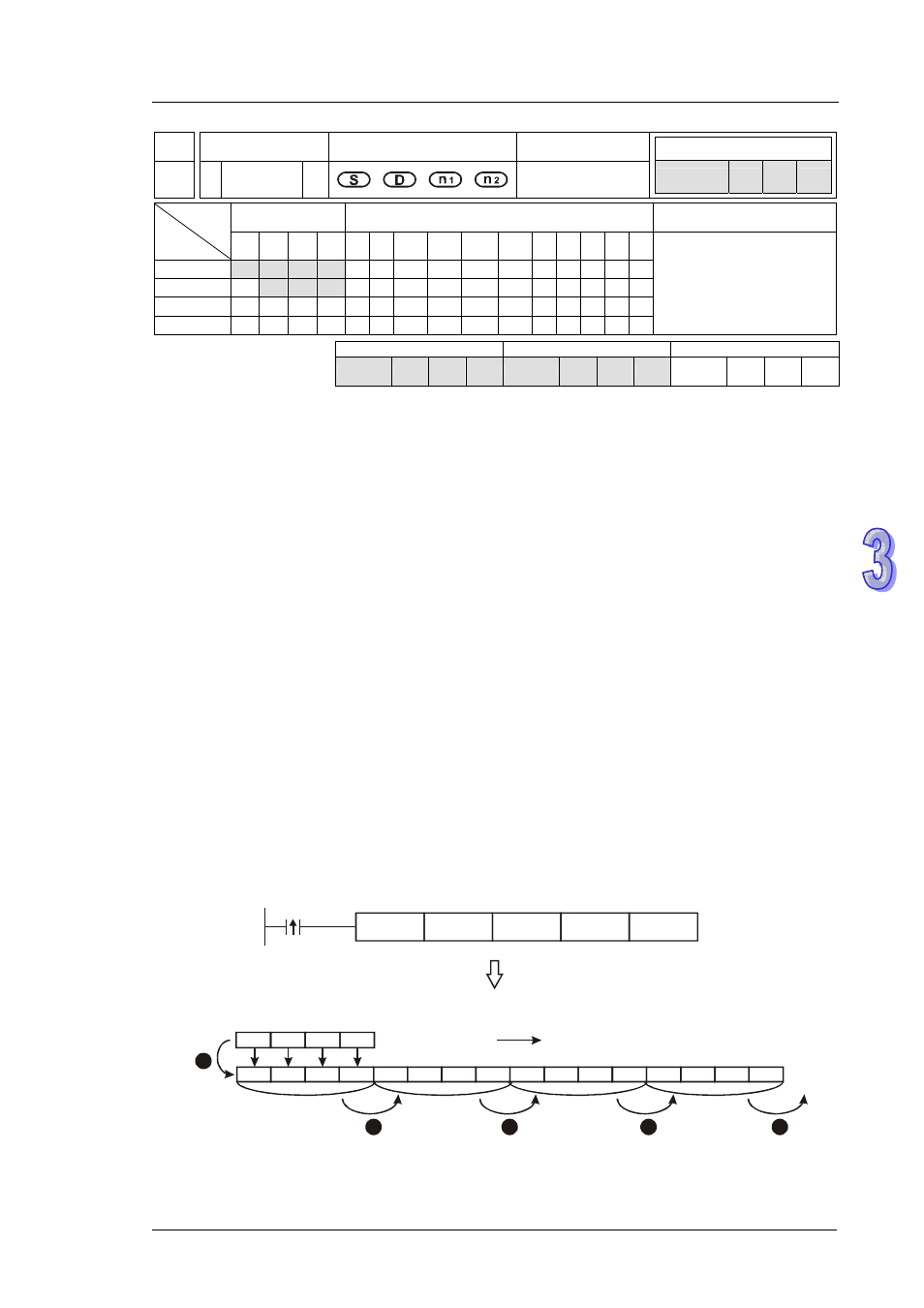

Operands:

S: Start No. of source device D: Start No. of destination device n

1

: Length of data to be

shifted n

2

: Number of bits to be shifted as a group

Explanation:

1.

This instruction performs a right shift from source device of n

2

bits starting from S to

destination device of n

1

bits starting from D.

2.

This instruction is generally used in pulse execution mode (SFTRP).

3.

Valid range of operand n1, n2 : 1

≤ n2 ≤ n1 ≤1024

Program Example:

1.

When X0 is rising edge triggered, SFTR instruction shifts X0~X4 into 16 bit data M0~M15

and M0~M15 also shift to the right with a group of 4 bits.

2.

The figure below illustrates the right shift of the bits in one scan.

n M3~M0

→ Carry

o M7~M4

→ M3~M0

p M11~M8

→ M7~M4

q M15~M12

→ M11~M8

r X3~X0

→ M15~M12 completed

X0

SFTR

X0

M0

K16

K4

X3

X2

X1

X0

M15 M14 M13 M12 M11 M10 M9

M8

M7

M6

M5

M4

M3

M2

M1 M0

1

2

3

4

5

4 bits in a group shift to the right

Carry