Delta DVP-ES2 User Manual

Page 166

D V P - E S 2 / S A 2 / S S 2 / S A2 / S X 2 / S E O p e r a t i o n M a n u a l - P r o g r a m m i n g

3 - 5 0

3.

Interrupt subroutines must be placed after the FEND instruction.

4.

Other interrupts are not allowed during execution of a current interrupt routine.

5.

When many interruptions occur, the priority is given to the firstly executed interruption. If

several interruptions occur at the same time, the priority is given to the interruption with the

smaller pointer No.

6.

Any interrupt request occurring between DI and EI instructions will not be executed

immediately. The interrupt will be memorized and executed when the next EI occurs.

7.

When using the interruption pointer, DO NOT repeatedly use the high-speed counter driven

by the same X input contact.

8.

When immediate I/O is required during the interruption, write REF instruction in the program

to update the status of I/O

Points to note:

Interrupt pointers (I):

a) External interrupts: 8 points including (I000/I001, X0), (I100/I101, X1), (I200/I201, X2),

(I300/I301, X3), (I400/I401, X4), (I500/I501, X5), (I600/I601, X6) and (I700/I701, X7) (00

designates interruption in falling-edge, 01 designates interruption in rising-edge)

b) Timer interrupts: 2 points including I605~I699 and I705~I799 (Timer resolution = 1ms)

c) High-speed counter interrupts: 8 points including I010, I020, I030, I040, I050, I060, I070, and

I080. (used with API 53 DHSCS instruction to generate interrupt signals)

d) Communication interrupts: 3 points including I140, I150 and I160

e) Associated

flags:

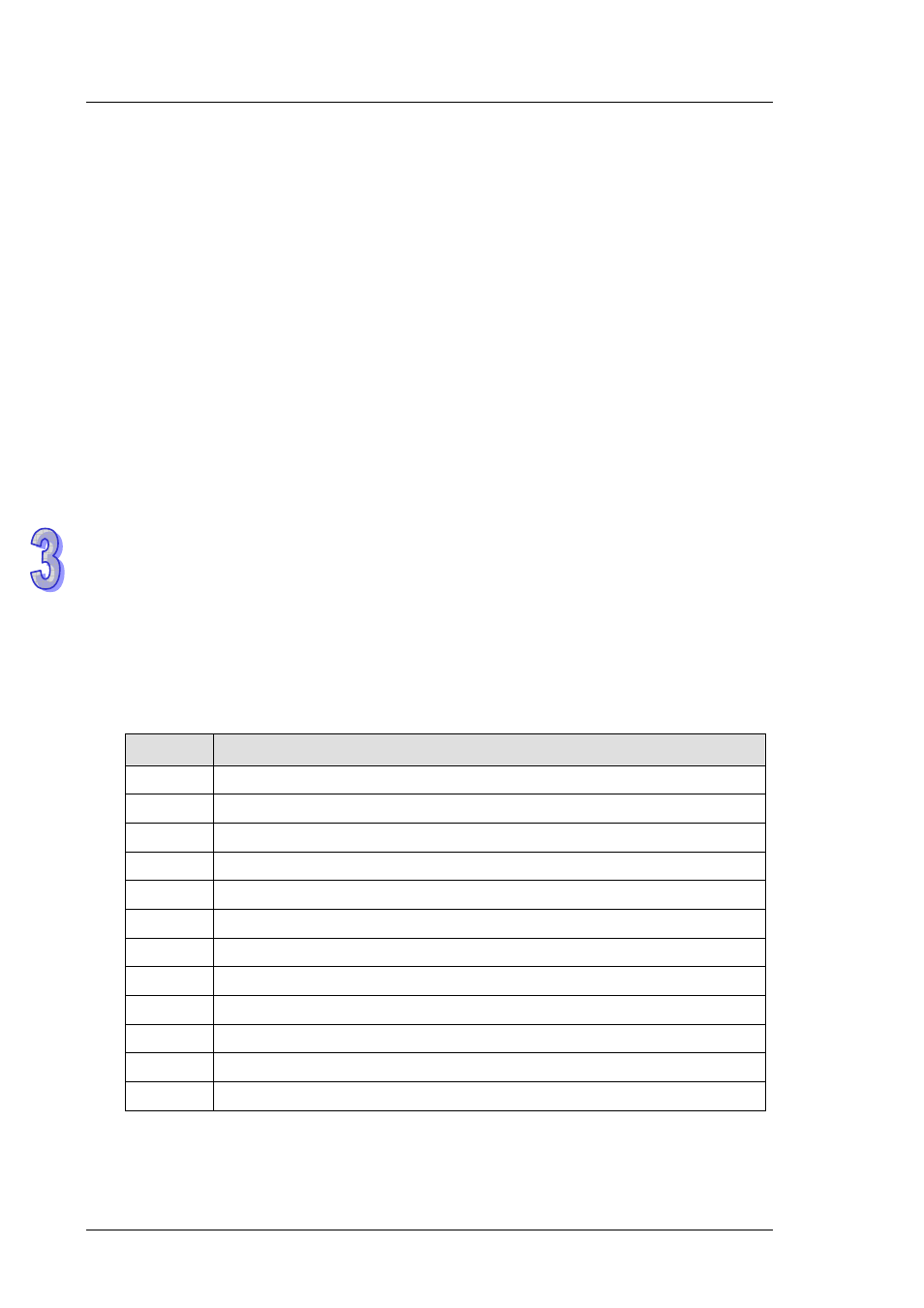

Flag

Function

M1050

Disable external interruption I000 / I001

M1051

Disable external interruption I100 / I101

M1052

Disable external interruption I200 / I201

M1053

Disable external interruption I300 / I301

M1054

Disable external interruption I400 / I401

M1055

Disable external interruption I500 / I501, I600 / I601, I700 / I701

M1056

Disable timer interrupts I605~I699

M1057

Disable timer interrupts I705~I799

M1059

Disable high-speed counter interruptions I010~I080

M1280

I000/I001 Reverse interrupt trigger pulse direction (Rising/Falling)

M1284

I400/I401 Reverse interrupt trigger pulse direction (Rising/Falling)

M1286

I600/I601 Reverse interrupt trigger pulse direction (Rising/Falling)

Note: Default setting of I000(X0) is falling-edge triggered. When M1280=ON and EI is enabled,

PLC will reverse X0 as rising-edge triggered. To reset X0 as falling-edge, reset M1280 first and