2 clock selection, 3 register description, 3 e1/t1 framer-liu – Artesyn ARTM-831X Installation and Use (June 2014) User Manual

Page 78: 2 clock selection 4.3.2.3 register description, Figure 4-9, Functional description

Functional Description

ARTM-831X Installation and Use (6806800M76E)

78

4.3.2.2

Clock selection

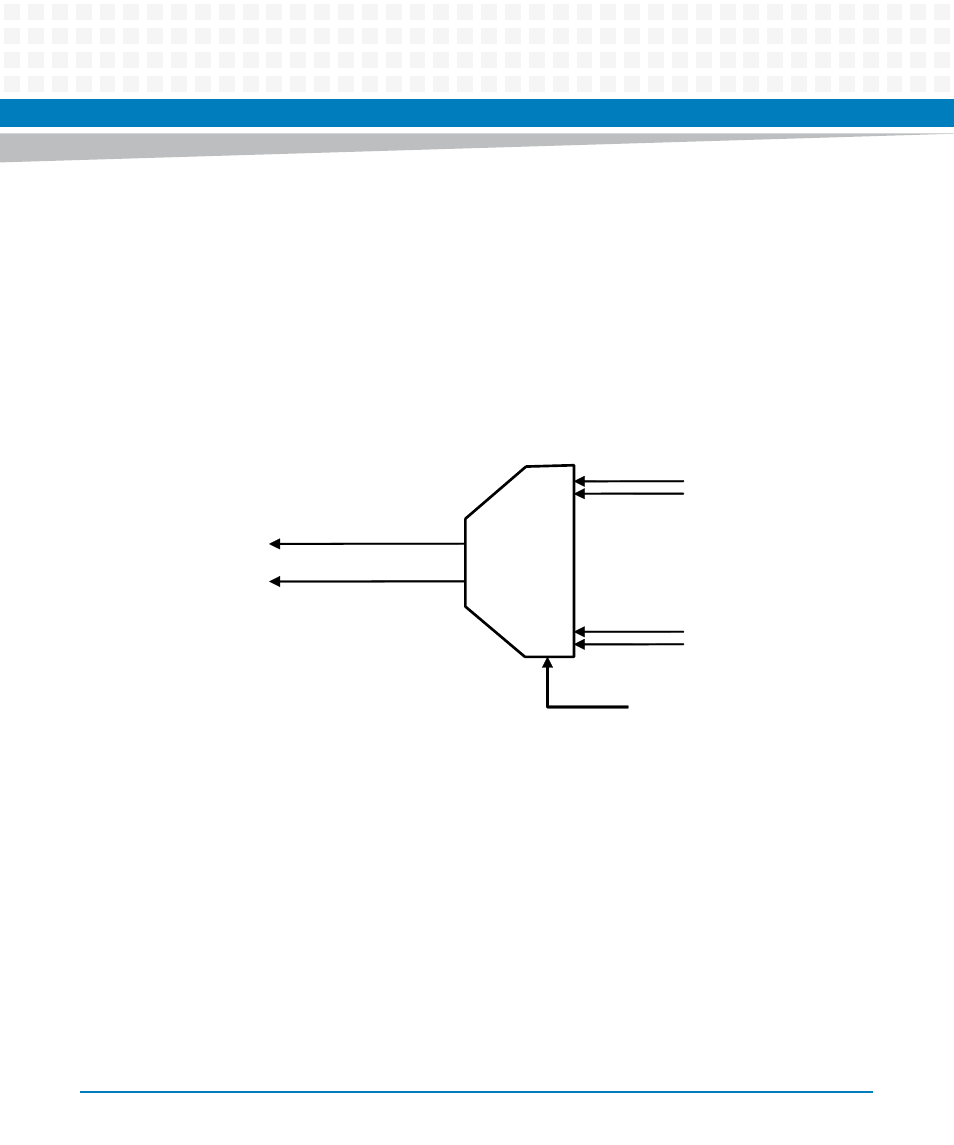

The E1/T1 mezzanine expansion unit provides a programmable reference clock selector unit.

The TSI-Extender FPGA device expands the capability of the clock selector of the TSI FPGA

device for the Framer 2 to 5. Two reference clocks out of 32 recovered receive clocks are pre-

selected and routed to the ARTM-831X base unit via the upper mezzanine connector. At the

ARTM-831X base unit they are connected to the clock selection unit in the FPGA_base device

and depending on its configuration forwarded to the system synchronizer located at the front

board. Each of the inputs is masked by on respective LOS alarm.

4.3.2.3

Register Description

For details, see

Chapter 10, EXT FPGA, on page 293

4.3.3

E1/T1 Framer-LIU

Six octal-E1/T1 EXAR XRT86VX38 Framer-LIU combo devices provide a total of 48 E1/T1 base

rate TDM interfaces on the ARTM-831X front panel through 3 VHDCI connectors. Each VHDCI

connector provides 16 E1/T1 line connections to the external world. Each framer is connected

to the TSI FPGA using H-MVIP interface for payload transactions and Local bus for control and

configuration. Monitoring/Alarm signals and recovered clocks are delivered to the TSI FPGA

and Ext FPGA.

Figure 4-9

E1/T1 mezzanine recovered receive clock selector unit

TDM RefClk 2

TDM_RefClk_3

To

ba

se bo

ard

vi

a

upp

er me

zza

ni

ne

conn

ect

o

r

32x recovered receive CLK

from E1/T1 Framer

Mask input on respective LOS Alarm

. . . . . . . .