Tsi fpga – Artesyn ARTM-831X Installation and Use (June 2014) User Manual

Page 180

TSI FPGA

ARTM-831X Installation and Use (6806800M76E)

180

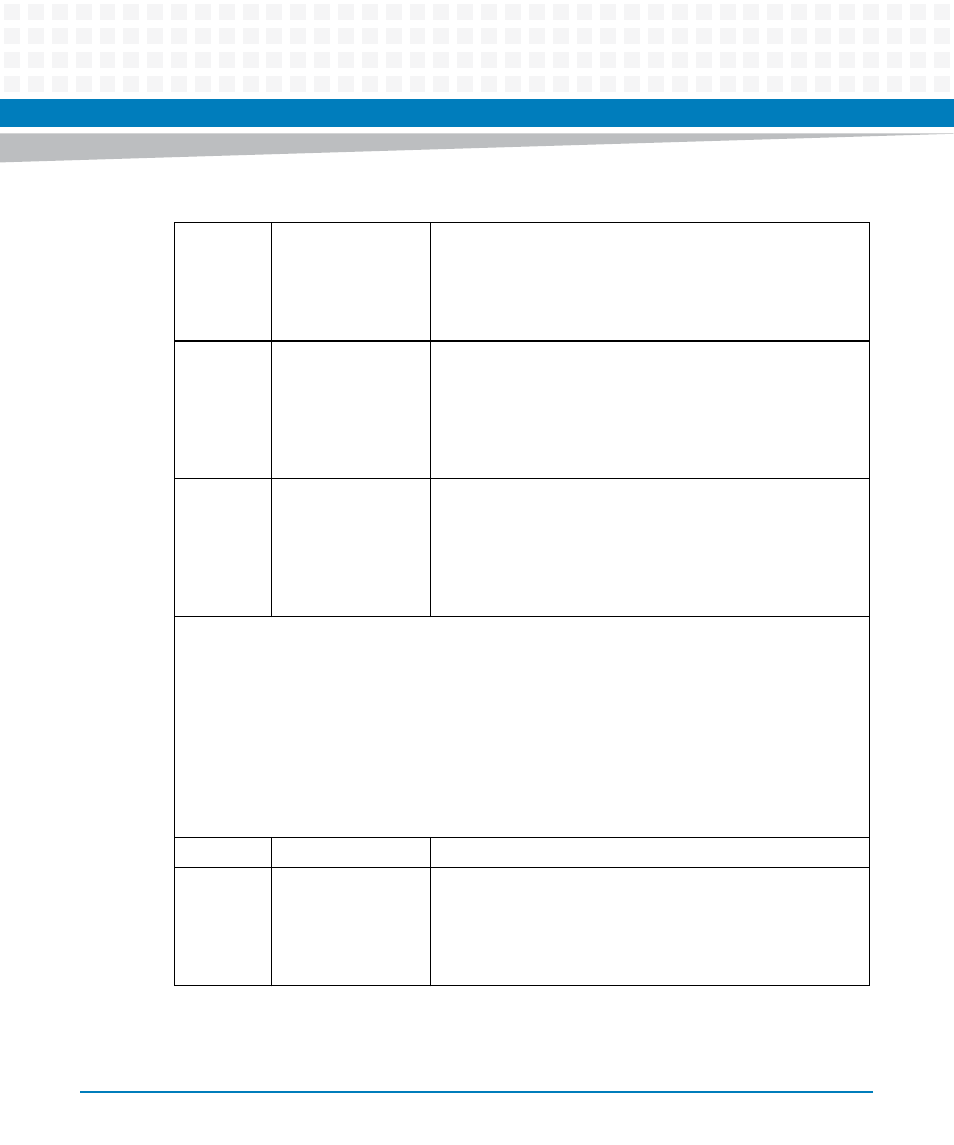

0x1101

0x1141

0x1181

SerDesTrmStatReg0

SerDesTrmStatReg1

SerDesTrmStatReg2

Serdes Transmitter Status Register (8bit) [Hw: syn , WAck1,

RAck1]

The Serdes transmitter status is shown.

Reg0 is for Serdes-connection to the BaseBoard, Reg1 to DMC1

and Reg2 to DMC2.

0x1102

0x1142

0x1182

SupplTstPatTrmReg

0

SupplTstPatTrmReg

1

SupplTstPatTrmReg

2

Supplemental Test Pattern Transmit Register (16bit) [Hw: asyn

, WAck4, RAck4]

Static Test Pattern transmitted via the supplementary channel

towards the serial interface.

Reg0 is for Serdes-connection to the BaseBoard, Reg1 to DMC1

and Reg2 to DMC2.

0x1104

0x1144

0x1184

SupplTstPatCrcDisp

GenCtrlReg0

SupplTstPatCrcDisp

GenCtrlReg1

SupplTstPatCrcDisp

GenCtrlReg2

Supplemental Test Pattern, CRC and Disparity Generator

Control Register (8bit) [Hw: asyn, WAck4, RAck4]

This registers control the test pattern, CRC and Disparity

transmission.

Reg0 is for Serdes-connection to the BaseBoard, Reg1 to DMC1

and Reg2 to DMC2.

Deserializer to TSI Allocater Block (Des2TsiBlk) [Hw: Cy1, InR, OutR]

The Tsi2SerBlk contains 3 converter blocks from Serdes links of DspFpgas. Each converter can put the

payload information of up to 30720 from DspFpga at the opposite side to incoming timeslots of the

TSI.

The received supplemental channel test pattern data can be read by using the registers of this block.

Furthermore the CRC status signals from the SerDes IP Block are evaluated and CRC and Disparity

errors are counted and indicated. The the link synchronization is controlled by registers of this block

too.

Access via SPI- bus from GlueFpga (occupies 256 Byte address area), hereof assigned to this block:

1200...12FF

Address

Acronym

Description

0x1200

0x1240

0x1280

SerDesRcvCtrlReg0

SerDesRcvCtrlReg1

SerDesRcvCtrlReg2

Serdes Receiver Control Register (8bit) [Hw: syn, WAck1,

RAck1]

A Serdes reset or resync can be initiated via this register.

Reg0 is for Serdes-connection to the BaseBoard, Reg1 to DMC1

and Reg2 to DMC2.

Table 9-5 RTM FPGA Address map Overview (continued)