Table 8-59, Artm telecom clock monitor time base register, Table 8-60 – Artesyn ARTM-831X Installation and Use (June 2014) User Manual

Page 150: Artm telecom clock monitor frequency register, Table 8-61, Artm telecom clock monitor lower limit register, Base artm fpga

Base ARTM FPGA

ARTM-831X Installation and Use (6806800M76E)

150

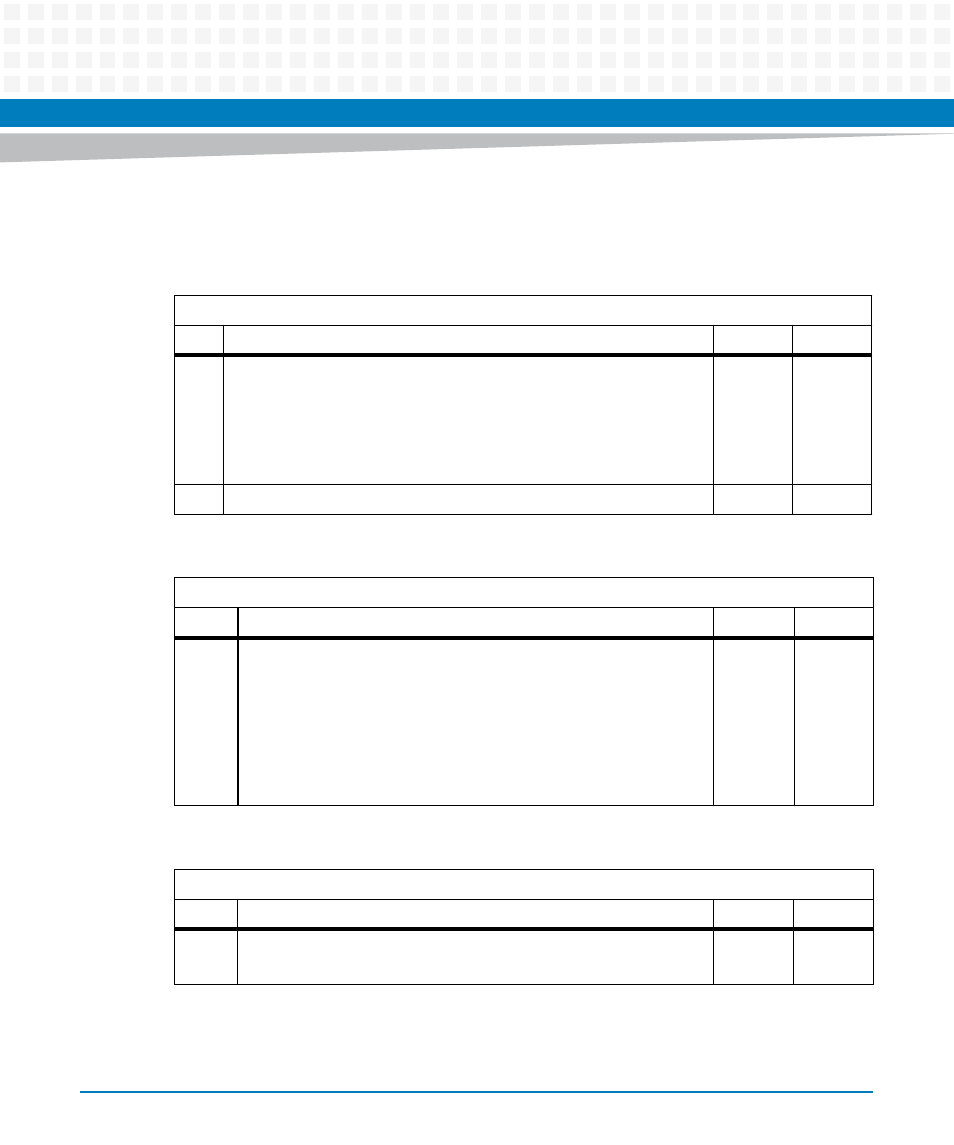

The following tables refer to the clock selected with Table ARTM Telecom Clock Monitor Select

Register

Table 8-59 ARTM Telecom Clock Monitor Time Base Register

Address: 0x25

Bit

Description

Default

Access

1:0

Select Time base for clock supervision:

0: Time Base is 0.5ms

1: Time Base is 64ms

2: Time Base is 1024ms

3: Time Base is 32.768s

0

RTM: r/w

7:2

Reserved

0

r

Table 8-60 ARTM Telecom Clock Monitor Frequency Register

Address: 0x26-0x27

Bit

Description

Default

Access

15:0

Number of rising clock edges of supervised Telecom Clock during

selected time base.

0: No clock edge sampled. Clock to slow for time base

1 - 65534: Number of sampled clocks during timer base.

65535: Overflow. Clock to fast for time base.

Note: Only valid when corresponding bit in Telecom Clock Monitor

Status Register is set.

0

RTM: r

Table 8-61 ARTM Telecom Clock Monitor Lower Limit Register

Address: 0x28-0x29

Bit

Description

Default

Access

15:0

Lower Limit for supervised Telecom Clock:

Used by Telecom Clock Monitor Out of Range Register.

0

RTM: r/w