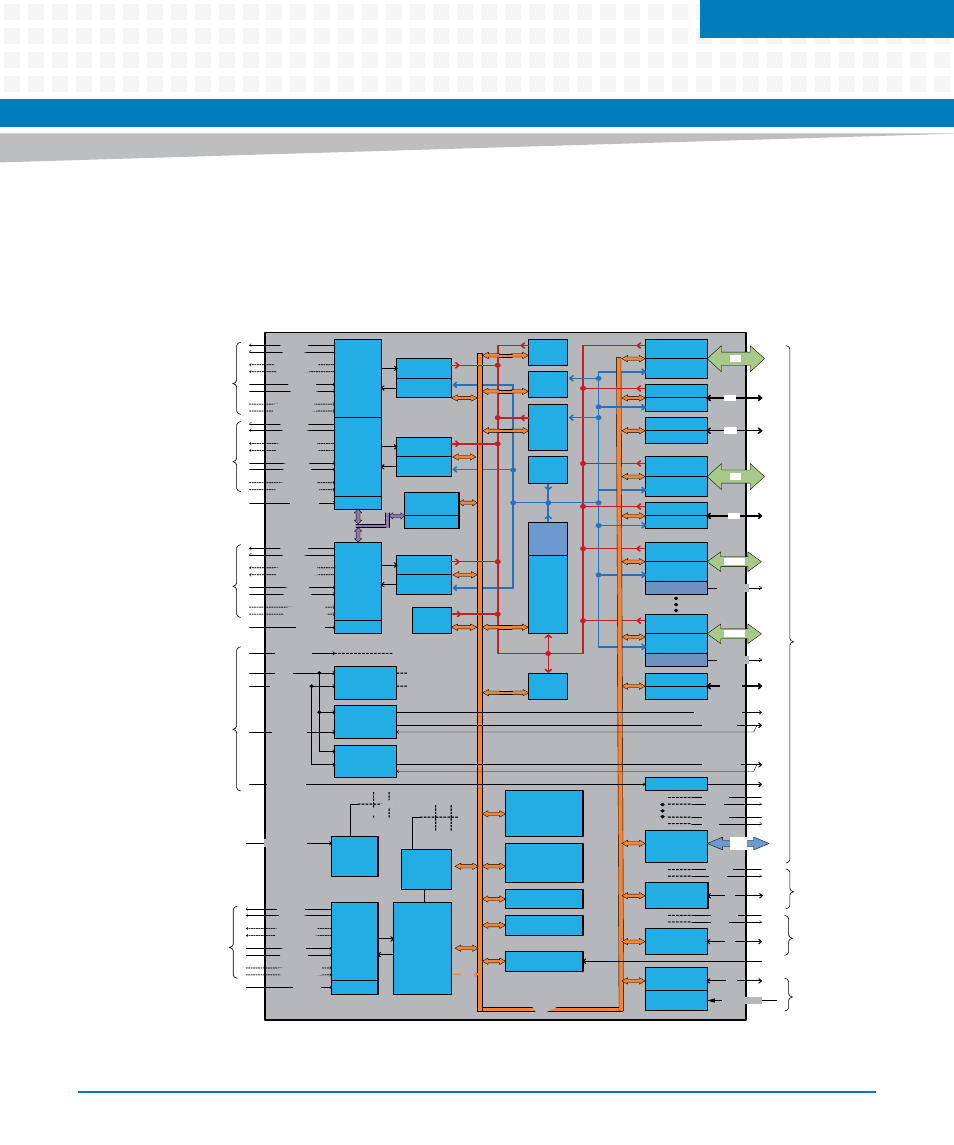

Tsi fpga, 1 architectural overview, Figure 9-1 – Artesyn ARTM-831X Installation and Use (June 2014) User Manual

Page 157: Architectural overview, Chapter 9, Figure 9-1 architectural overview

Chapter 9

ARTM-831X Installation and Use (6806800M76E)

157

TSI FPGA

9.1

Architectural Overview

Figure 9-1

Architectural Overview

SBI

DSP

FPGA

0

SERDES

QUAD

0

Channel

0 (+1)

2nd

link

as

prep

arat

ion

2nd

link

as

prep

arati

on

2.5G

Bit

Tx

2.5G

Bit

Rx

DSP

FPGA

1

SERDES

QUAD

0

Channel

2 (+3)

2nd

link

as

prep

arat

ion

2nd

link

as

prep

arat

ion

2.5G

Bit

Tx

2.5G

Bit

Rx

DSP

FPGA

2

SERDES

QUAD

1

Channel

0 (+1)

2nd

link

as

prep

arat

ion

2nd

link

as

prep

arat

ion

2.5G

Bit

Tx

2.5G

Bit

Rx

Ser2Tsi0

Tsi2Ser0

Ser2Tsi1

Tsi2Ser1

Ser2Tsi2

Tsi2Ser2

TSI

Sbi2Tsi0

Tsi2Sbi0

RToh2Tsi0

Tsi2TToh0

Sbi2Tsi1

Tsi2Sbi1

RToh2Tsi1

Tsi2TToh1

HMvip2Tsi0

Tsi2HMvip0

HMvip2Tsi5

Tsi2HMvip5

SERDES

QUAD

2

Channel

0 (+1)

Host

PCIE

Bridge

2nd

link

as

prep

arat

ion

2nd

link

as

prep

arat

ion

2.5G

Bit

Tx

2.5G

Bit

Rx

RFClk

RFClk

RFClk

125MHz

125MHz

100MHz

Pcie2Wshb

Wshb2

Lc16_8Bs

Wshb2Cfg

Intrpt2Pci

e

RstGnrt

SBI

Toh

Toh

HMVIP

HMVIP

Poh

PowerGood

Wshb2Spi0

Wshb2Spi1

Telecom

clocks

Int

er

ru

pts

Local

Bus

Interrupt

Reset

Interrupt

Reset

Interrupt

Reset

Interrupt

Reset

SPI

SPI

Framer:

2x

PMC8310 *)

6x

XRT86 *)

Line

Interfaces:

4x

XRT75 *)

*) not all

interfaces

may be

actually

connected to

pins dep. on

RTM variant

Bits-

Elements

SPI

Ext

FPGA

Config

Flash

Diebel, Tieto 26.03.2010

RPoh2Mfs0

Mfs2TPoh0

Ch0

Pat

W

ish

bo

ne

Sla

ve

B

us

32

Bi

t

125

Mh

z

Wshbn2

SrdBs

AdrExtn

Serd

es

Clien

t

Inte

rface

Bus

MfsModes

MfsModes

General

Registers

General

Test

Registers

Gr8

Ins

Extr

Destroy

Working

ForceGolden

clk

RtmFpga

Version

RTM ID

Clk, FrSync

Gnrtr (PLL)

131M072

int. work fs 8kHz

SpBi

InsIdle

Pattern

SpBo

TpGen

Ext

TpGen

Int

TpCmp

Int

TpCmp

Ext

Clk, FrSync

Gnrtr (PLL)

77M76

Clk,FrSync

Gnrtr (PLL)

16M384

77.76MHz

8kHz

166.666Hz

32.768MHz

int. work clk 131M072

12.288MHz

12.288MHz

T12Mfs

Mfs2T1

77.76MHz

16.384MHz

MfsT1

Ma

in

Re

set

RtmExt

MatchVersion

MfsXrt86

MfsXrt86

MfsPmC8310