Tsi fpga – Artesyn ARTM-831X Installation and Use (June 2014) User Manual

Page 179

TSI FPGA

ARTM-831X Installation and Use (6806800M76E)

179

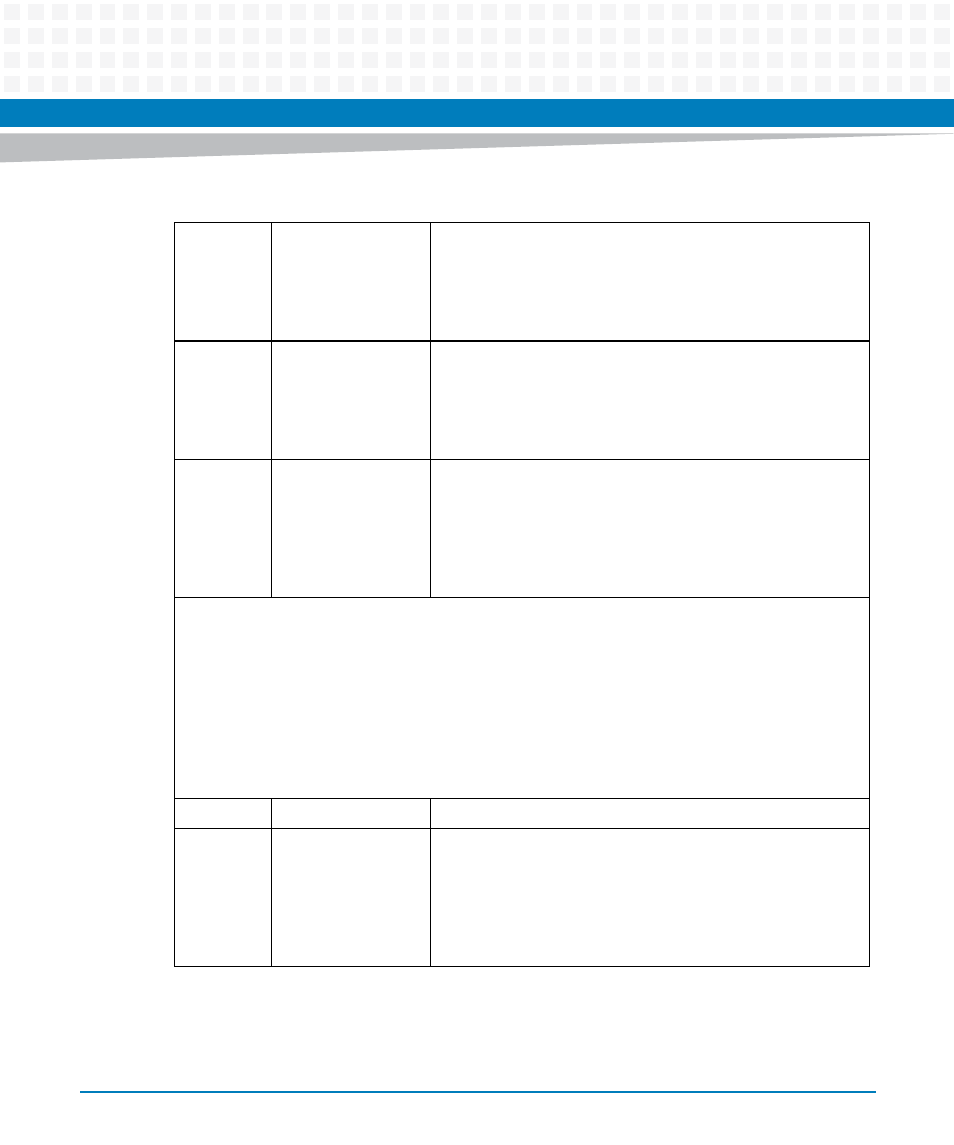

0x10C4

0x10E4

TstPatCmpCtrlReg0

TstPatCmpCtrlReg1

Test Pattern Comparator Control Register (8bit) [Hw: asyn,

WAck4, RAck4]

This registers enables either static or pseudo random pattern

reception.

0x10C8

0x10E8

TstPatCmpSyncStaR

eg0

TstPatCmpSyncStaR

eg1

Test Pattern Synchronization Status Register (32bit ) [Hw: asyn

, WAck4, RAck4]

This registers indicates the status of the receiver for static

pattern or the PRBS bit stream.

0x10CC

0x10EC

TstPatCmpErrorCntR

eg0

TstPatCmpErrorCntR

eg1

Test Pattern Comparator Error Count Register (32bit) [Hw: asyn

, WAck4, RAck4]

After synchronization of the static pattern or the PRBS receiver

this registers counts bit errors. The counter sticks at 0xFFFFFF.

It is cleared, when TstPatCmpRxPatEn bit changes from 0 to 1.

i.e. the receiver is re-enabled again.

Tsi to Serdes Converter Block (Tsi2SerBlk) [Hw: Cy1, InR, OutR]

The Tsi2SerBlk contains 3 converter blocks to Serdes links to DspFpgas. Each converter can pick the

payload information of up to 30720 outgoing timeslots of the TSI and transfer them to a DspFpga at

the opposite side.

For static test pattern transmission a supplementary channel is provided. The supplementary channel

has a data rate of 128kbit/s because of the transmission of 16 bits every 125 μs. Furthermore the

Tsi2SerBlk controls the link synchronization and the CRC, Disparity insertion of the SerDes IP Block.

Access via SPI- bus from GlueFpga (occupies 256 Byte address area), hereof assigned to this block:

1100...11FF

Address

Acronym

Description

0x1100

0x1140

0x1180

SerDesTrmCtrlReg0

SerDesTrmCtrlReg1

SerDesTrmCtrlReg2

Serdes Transmitter Control Register (8bit) [Hw: syn , WAck1,

RAck1]

A Serdes transmitter reset or resync can be initiated via this

register.

Reg0 is for Serdes-connection to the BaseBoard, Reg1 to DMC1

and Reg2 to DMC2.

Table 9-5 RTM FPGA Address map Overview (continued)