Tsi fpga – Artesyn ARTM-831X Installation and Use (June 2014) User Manual

Page 190

TSI FPGA

ARTM-831X Installation and Use (6806800M76E)

190

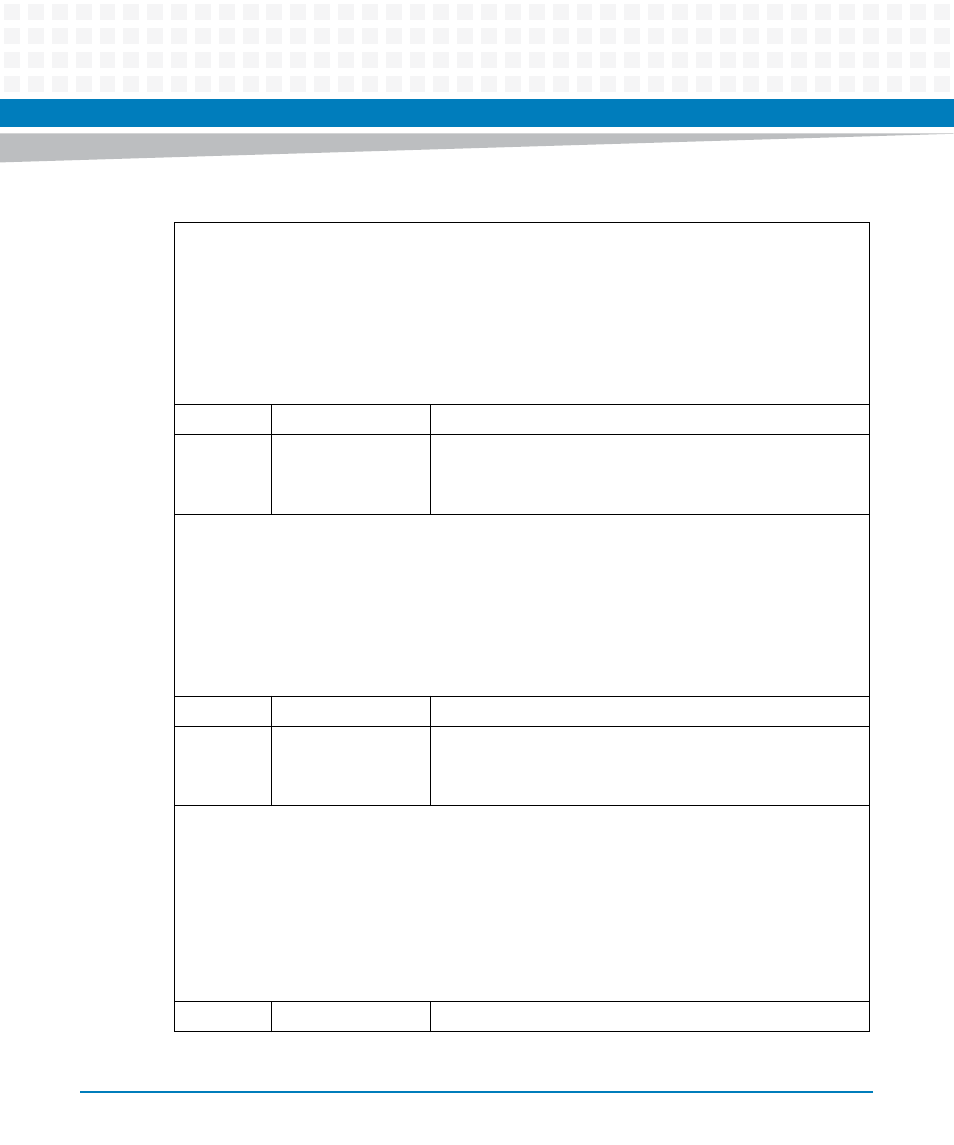

External components accessed through RTM FPGA as bridge to SPI bus 1 (ExtBridgedCompSpi1) [Hw:

Cy1, InR, OutR]

The RTM Fpga bridges the PCI Bus to SPI Bus 1. The SPI interface of the ExtFpga on the RTM-Module

components is connected to this bus. The bus width is adapted automatically to the needs of the

accessed component.

Access via PCI-bus 512kByte non-prefetchable memory area of 64bit-bar[3,2]

bridged to SPI bus 1, where the ExtFpga on the RTM-Module is connected, hereof assigned to this

block: 3000...3FFF

Address

Acronym

Description

0x3000

...

0x3FFF

ExtFpgaChip

ExtFpga Registers (access redirected to SPI interface)

Refer register description, chapter ExtFpga, occupied area 0xFF,

16 times replicated

External components accessed through Rtm FPGA as bridge to SPI bus 2 (ExtBridgedCompSpi2) [Hw:

Cy1, InR, OutR]

The RTM Fpga bridges the PCI Bus to SPI Bus 2, HW signals are used commonly with SPI Bus

3(multiplexed). The SPI interfaces to a BaseExtFpga components which are connected to this bus. The

bus width is adapted automatically to the needs of the accessed component.

Access via PCI-bus 512kByte non-prefetchable memory area of 64bit-bar[3,2]

bridged to SPI bus 2, where 2 DS26503 framers on BaseExtFpga are connected, hereof assigned to this

block: 4000...4FFF

Address

Acronym

Description

0x4000

...

0x4FFF

BaseExtFpgaChip

BaseExtFpga Registers (access redirected to SPI interface)

Refer to BaseExtFpga chapter for register description, occupied

area 0xFF, 16 times replicated

External components accessed through RTM FPGA as bridge to SPI bus 3 (ExtBridgedCompSpi3) [Hw:

Cy1, InR, OutR]

The RTM Fpga bridges the PCI Bus to SPI Bus 3, HW signals are used commonly with SPI Bus 2

(multiplexed). The SPI interfaces to 2x DS26503 components which are connected to this bus. The

BaseExtFpga routes the Spi-Bus directly to the Ds26503 components and bypasses its internal bus.

The bus width is adapted automatically to the needs of the accessed component.

Access via PCI-bus 512kByte non-prefetchable memory area of 64bit-bar[3,2] bridged to SPI bus 2,

where 2 DS26503 framers adn on BaseExtFpga are connected, hereof assigned to this block:

5000...7FFF

Address

Acronym

Description

Table 9-5 RTM FPGA Address map Overview (continued)