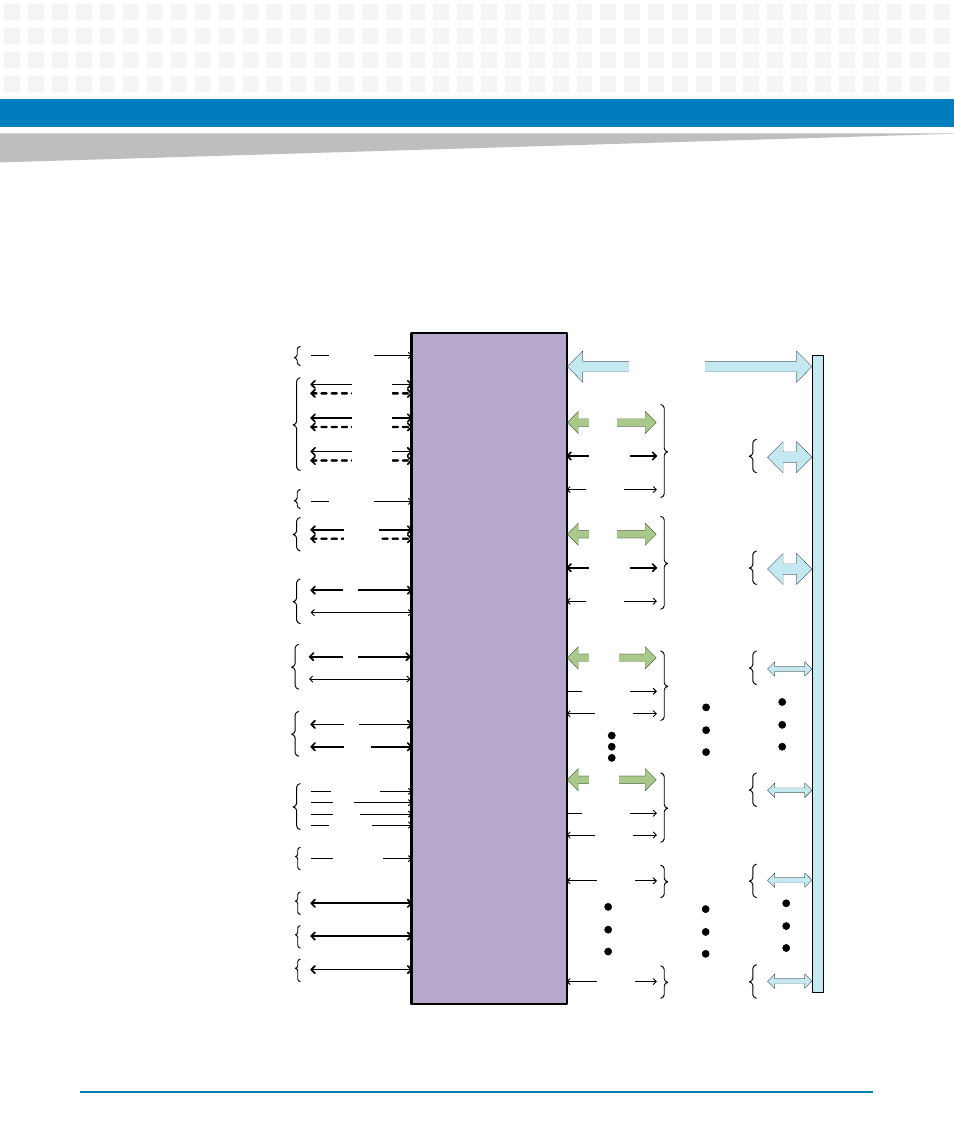

3 tsi fpga signals overview, Figure 9-2, Overview of tsi fpga signals – Artesyn ARTM-831X Installation and Use (June 2014) User Manual

Page 162: Rtm fpga, Tsi fpga, Figure 9-2 overview of tsi fpga signals

TSI FPGA

ARTM-831X Installation and Use (6806800M76E)

162

9.3

TSI FPGA Signals Overview

Figure 9-2

Overview of TSI FPGA Signals

SerDes links to Dsp-

pools on baseboard

and 2 submodules

2.5Gb or

2x1.25Gb

2.5Gb or

2x1.25Gb

2.5Gb or

2x1.25Gb

PCIE1.0

x1 or x2

PCIE links to host

bridgeD

2x Interrupt ,

2x Reset

2x DS26503 Bits

framer

SPI

Interrupt,

Reset

ExtFpga pin

extention

SPI

Serial Configuration

Flash

SPI

Config

Glue Fpga

6x tbd.

Led, Debug

Leds, DebugPins

32.768MHz

8kHz

166Hz

Reference Clock

2x125MHz

Reference Clock

1x100MHz

Basic TDM clock,

Framesync and

Multiframesync

Basic Reset

PowerGood

Test

Jtag

16Bit Addressbus,

16Bit Databus,

Rd, Wr, 8xCs,Rdy

PMC8310

Framer 0

SBITR

Bus 0

Overhead

Interface

77.76MHz

HMVIP

Bus 0

32.768MHz

Xrt86

Framer 0

HMVIP

Bus 5

32.768MHz

Xrt86

Framer 5

Interrupt,

Reset

Interrupt,

Reset

SBITR

Bus 1

Overhead

Interface

PMC8310

Framer 1

Interrupt,

Reset

Interrupt,

Reset

Xrt75

Liu0

Interrupt ,

Reset

Xrt75

Liu0

Interrupt ,

Reset

16Bit Data

16Bit Data

8Bit Data

8Bit Data

8Bit Data

8Bit Data

RTM

FPGA

- ARTM-9405 16x10GbE Installation and Use Guide (May 2014) (64 pages)

- ATCA 7370 / ATCA 7370-S Installation and Use (January 2015) (256 pages)

- ATCA 7370 / ATCA 7370-S Installation and Use (September 2014) (254 pages)

- ATCA-7350 - Integrating with Workbench User Guide (September 2014) (34 pages)

- ATCA-7350 Installation and Use (September 2014) (208 pages)

- ATCA-7365-CE Installation and Use (Jan 2015) (300 pages)

- ATCA-7365-CE Installation and Use (May 2014) (294 pages)

- ATCA-7365-CE Installation and Use (May 2014) (306 pages)

- ATCA-7368 Installation and Use (June 2014) (222 pages)

- ATCA-7475 Installation and Use (October 2014) (284 pages)

- ATCA-7480 Installation and Use (April 2015) (330 pages)

- ATCA-8330 Installation and Use (April 2015) (236 pages)

- ATCA-8320 Installation and Use (May 2014) (456 pages)

- ATCA-9305 User's Manual (May 2014) (270 pages)

- ATCA-9405 Installation and Use (October 2014) (168 pages)

- ATCA-F120 Installation and Use (August 2014) (122 pages)

- ATCA-F140 Installation and Use (September 2014) (138 pages)

- ATCA-MF106 Installation and Use (September 2014) (86 pages)

- Centellis-4440/AXP1440 Installation and Use (September 2014) (208 pages)

- Centellis 4410 (AXP-1410) Installation and Use (July 2014) (202 pages)

- Centellis 2100 Release 3.0 Installation and Use (March 2015) (192 pages)

- Centellis 2100 Release 3.0 Installation and Use (March 2015) (176 pages)

- Centellis 2000 User Card-10GE Installation and Use (May 2014) (54 pages)

- Centellis 2000 User Card-10GE with Telco Alarm Installation and Use (May 2014) (60 pages)

- COMX-CAR-210 Installation and Use (August 2014) (76 pages)

- COMX-P1022 Installation and Use (July 2014) (84 pages)

- COMX-P2020 Installation and Use (February 2015) (100 pages)

- COMX-CORE Series Installation and Use (August 2014) (128 pages)

- COMX-P2020 Installation and Use (July 2014) (100 pages)

- COMX-P4080-2G-ENP2 Installation and Use (August 2014) (70 pages)

- COMX-P4080 Installation and Use (August 2014) (126 pages)

- COMX-P40x0 ENP2 Installation and Use (August 2014) (130 pages)

- COMX-P40x0 ENP2 Installation and Use (January 2015) (140 pages)

- iVPX7225 RTM Installation and Use (April 2015) (56 pages)

- MITX-430/MITX-440-DVI-2E Installation and Use (August 2014) (118 pages)

- CPCI-6200 Installation and Use (May 2015) (234 pages)

- SCP-MITX-CORE-820-SM Installation and Use (August 2014) (132 pages)

- iVPX7225 Installation and Use (April 2015) (168 pages)

- MVME2502 Installation and Use (August 2014) (150 pages)

- MVME2502 Installation and Use (December 2014) (166 pages)

- MVME2500 VxWorks 6.8 AMP User Guide (August 2014) (40 pages)

- MVME2500 VxWorks 6.8 User Guide (April 2014) (44 pages)

- MVME3100 Single Board Computer Installation and Use (June 2014) (156 pages)

- MVME4100 Single Board Computer Installation and Use (June 2014) (136 pages)