Tsi fpga – Artesyn ARTM-831X Installation and Use (June 2014) User Manual

Page 236

TSI FPGA

ARTM-831X Installation and Use (6806800M76E)

236

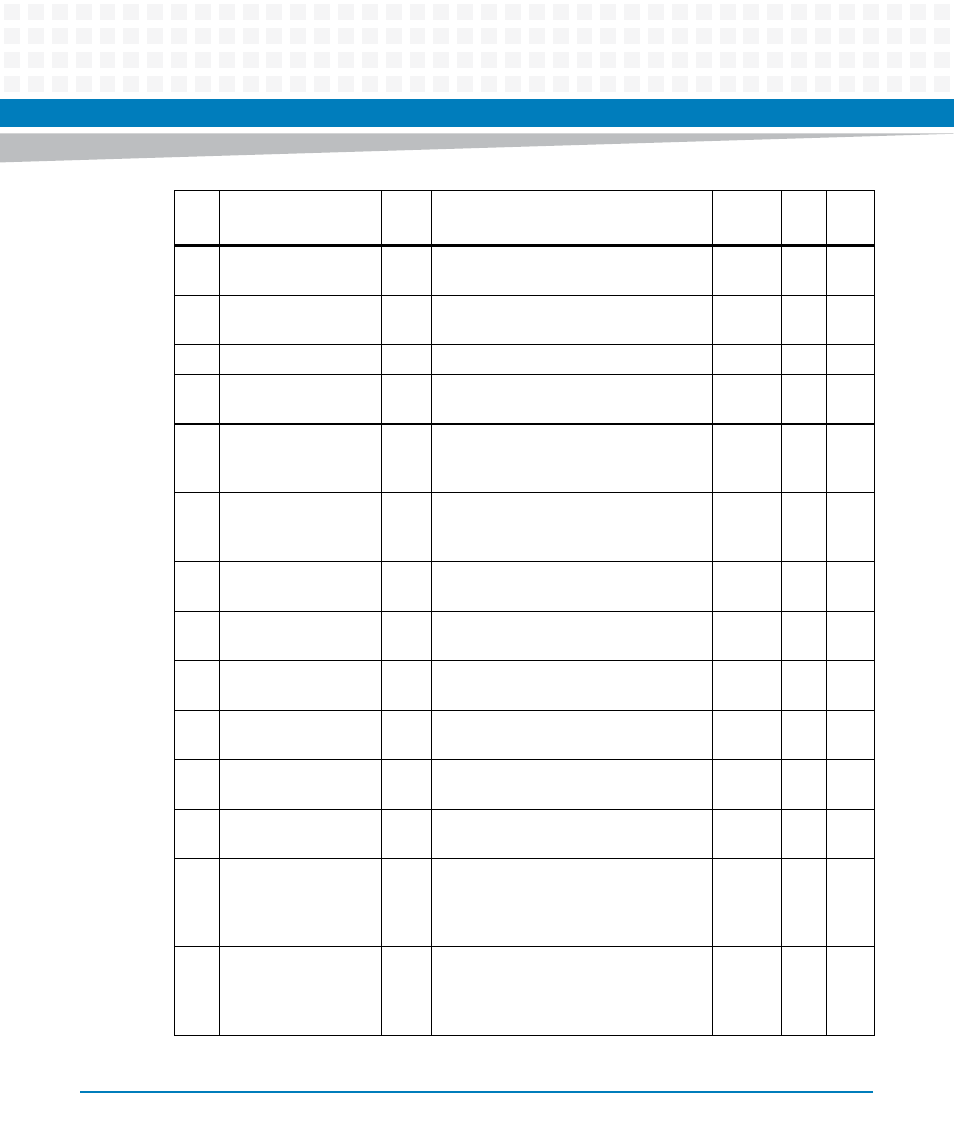

27

Spi2BusRdyTmOutRe

s

RW

0b1: Spi2BusRdyTmOutRes, reset

ready timeout at Spi bus 2 indicator

0b0

X

X

26

Spi1BusRdyTmOutRe

s

RW

0b1: Spi1BusRdyTmOutRes, reset

ready timeout at Spi bus 1 indicator

0b0

X

X

25

-

-

reserved

undef

-

-

24

LcBusRdyTmOutRes

RW

0b1: LcBusRdyTmOutRes, reset ready

timeout at local bus indicator

0b0

-

-

23

ParErrDrpSbi1Res

RW

0b1: ParErrDrpSbi1Res, reset parity

error in SBI drop data from Sonet/Sdh-

framer1 indicator

0b0

X

X

22

ParErrDrpSbi0Res

RW

0b1: ParErrDrpSbi0Res, reset parity

error in SBI drop data from Sonet/Sdh-

framer0 indicator

0b0

X

X

21

SerdesRcvErrorRes2

RW

0b1: SerdesRcvErrorRes2, reset the

serdes receiver2 error indicator

0b0

X

X

20

SerdesRcvErrorRes1

RW

0b1: SerdesRcvErrorRes1, reset the

serdes receiver1 error indicator

0b0

X

X

19

SerdesRcvErrorRes0

RW

0b1: SerdesRcvErrorRes0, reset the

serdes receiver0 error indicator

0b0

X

X

18

SerdesTrmErrorRes2

RW

0b1: SerdesTrmErrorRes2, reset the

serdes transmitter2 error indicator

0b0

X

X

17

SerdesTrmErrorRes1

RW

0b1: SerdesTrmErrorRes1, reset the

serdes transmitter1 error indicator

0b0

X

X

16

SerdesTrmErrorRes0

RW

0b1: SerdesTrmErrorRes0, reset the

serdes transmitter0 error indicator

0b0

X

X

15

NoTTPohFrameSync

1Res

RW

0b1: NoTTPohFrameSync1Res, reset

no transmit transport path overhead

frame sync pulse from Sonet/Sdh-

framer1 indicator

0b0

X

X

14

NoTTPohFrameSync

0Res

RW

0b1: NoTTPohFrameSync0Res, reset

no transmit transport path overhead

frame sync pulse from Sonet/Sdh-

framer0 indicator

0b0

X

X

Bit

Acronym

Type

Description

Default

Pwr

Soft